# Next Gen Infrastructure Core (NGIC) & M-CORD

Christian Maciocco Principal Engineer, Director of Telecom Systems Research – Intel Labs

Ashok Sunder Rajan, Kannan Babu Ramia, Sai Edupuganti, Jacob Cooper, Karla Saur – Intel Labs

CORD Build Event - November 7-9th, 2017 – San Jose, CA

Intel Labs

# Legal Disclaimer

- This presentation contains the general insights and opinions of Intel Corporation ("Intel"). The information in this presentation is provided for information only and is not to be relied upon for any other purpose than educational. Use at your own risk! Intel makes no representations or warranties regarding the accuracy or completeness of the information in this presentation. Intel accepts no duty to update this presentation based on more current information. Intel is not liable for any damages, direct or indirect, consequential or otherwise, that may arise, directly or indirectly, from the use or misuse of the information in this presentation.

- Intel technologies' features and benefits depend on system configuration and may require enabled hardware, software or service activation. Learn more at intel.com, or from the OEM or retailer.

- No license (express or implied, by estoppel or otherwise) to any intellectual property rights is granted by this document.

- Intel, the Intel logo and Xeon are trademarks of Intel Corporation in the United States and other countries. \*Other names and brands may be claimed as the property of others.

- © 2017 Intel Corporation.

# Agenda

- vEPC Background

- Next Generation Infrastructure Core (NGIC)

- CORD High Level View

- NGIC and M-CORD

- Summary / Next Steps

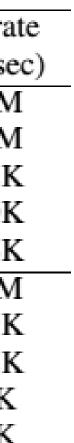

## vEPC Background (1/2)

- Operators' real traffic (San Jose, Houston, Chicago, ...)

- Identified system's bottleneck

- "Understanding Bottlenecks in Virtualizing Cellular Core Network functions", IEEE LANMAN '15

- No independent control or data plane scaling

"Other names and brands may be claimed as the property of others"

Intel Labs

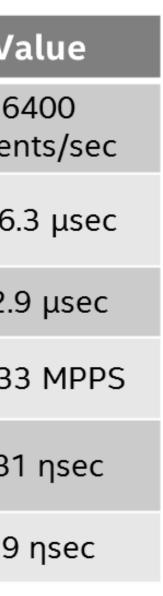

| Dimension     | Parameter        | Description                                             | V         |

|---------------|------------------|---------------------------------------------------------|-----------|

| Control Plane | ٨ <sub>c</sub>   | NAS event arrival rate                                  | 6<br>ever |

|               | Τ <sub>C</sub>   | Total time event spends in the system (Service + Wait)  | 156       |

|               | S <sub>TWC</sub> | Average event wait time                                 | 42.9      |

| User Plane    | λ <sub>υ</sub>   | Packet arrival rate                                     | 5.53      |

|               | Τ <sub>υ</sub>   | Total time packet spends in the system (Service + Wait) | 181       |

|               | S <sub>TWU</sub> | Average packet wait time                                | 29        |

**Control & User Plane Simulation Parameters**

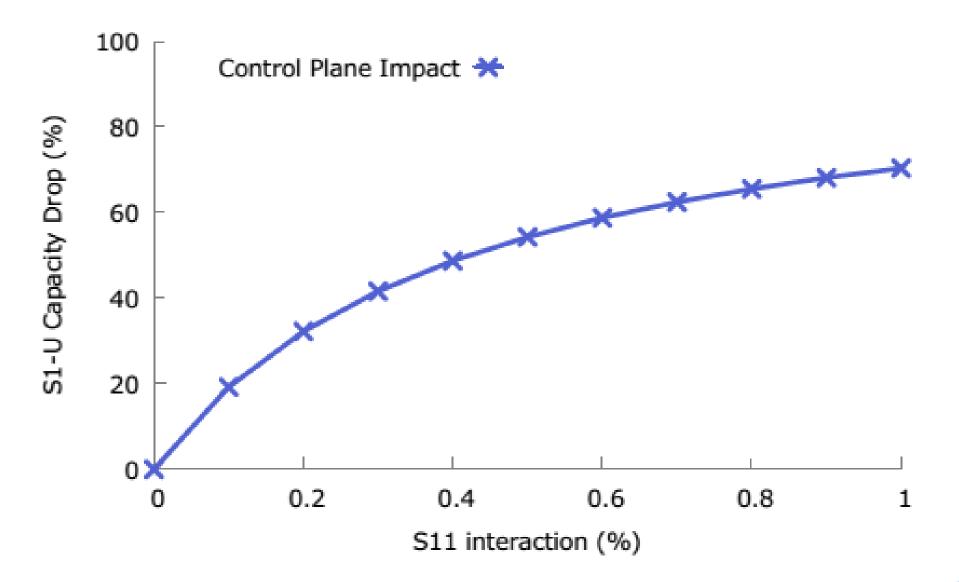

User plane capacity reduction as control plane interference increases

# vEPC Background (2/2)

**EPC Setup**

"Other names and brands may be claimed as the property of others"

Intel Labs

| d                                 |  |

|-----------------------------------|--|

|                                   |  |

| <b>pp</b><br>rver<br>deo,<br>b)   |  |

|                                   |  |

|                                   |  |

|                                   |  |

|                                   |  |

| App<br>erver<br><sup>Video,</sup> |  |

| App<br>erver<br><sup>Video,</sup> |  |

| App<br>erver                      |  |

| Direction | Traffic type | Traffic mix | Pkt size | Pkt ra  |

|-----------|--------------|-------------|----------|---------|

|           |              | %           | (bytes)  | (pkt/se |

| Downlink  | VoLTE        | 5.1         | 72       | 2.1N    |

|           | Web          | 52.2        | 1200     | 1.3N    |

|           | Video        | 29.5        | 1440     | 602F    |

|           | Apps         | 6.7         | 675      | 2901    |

|           | Email/other  | 6.7         | 1440     | 1361    |

| Uplink    | VoLTE        | 32.3        | 72       | 2.1N    |

|           | Web          | 43.1        | 690      | 289F    |

|           | Video        | 12.1        | 240      | 232F    |

|           | Apps         | 6.5         | 400      | 76K     |

|           | Email/other  | 6.2         | 1000     | 29K     |

|           | •            | •           | -        | •       |

**User Plane Traffic Model**

# Agenda

- vEPC Background

- Next Generation Infrastructure Core (NGIC)

- CORD High Level View

- NGIC and M-CORD

- Summary / Next Steps

## Next Generation Infrastructure Core (NGIC)

### What is it ? Why ?

- Research and collaborations to understand telecom workloads behavior on Intel Architecture

- Research to address software/hardware platform improvements

- Released learnings and optimized reference software into open source community (DPDK, CORD)

- S/P-GW, Cuckoo Hash for optimized lookup from collaborations with industry or academic partners

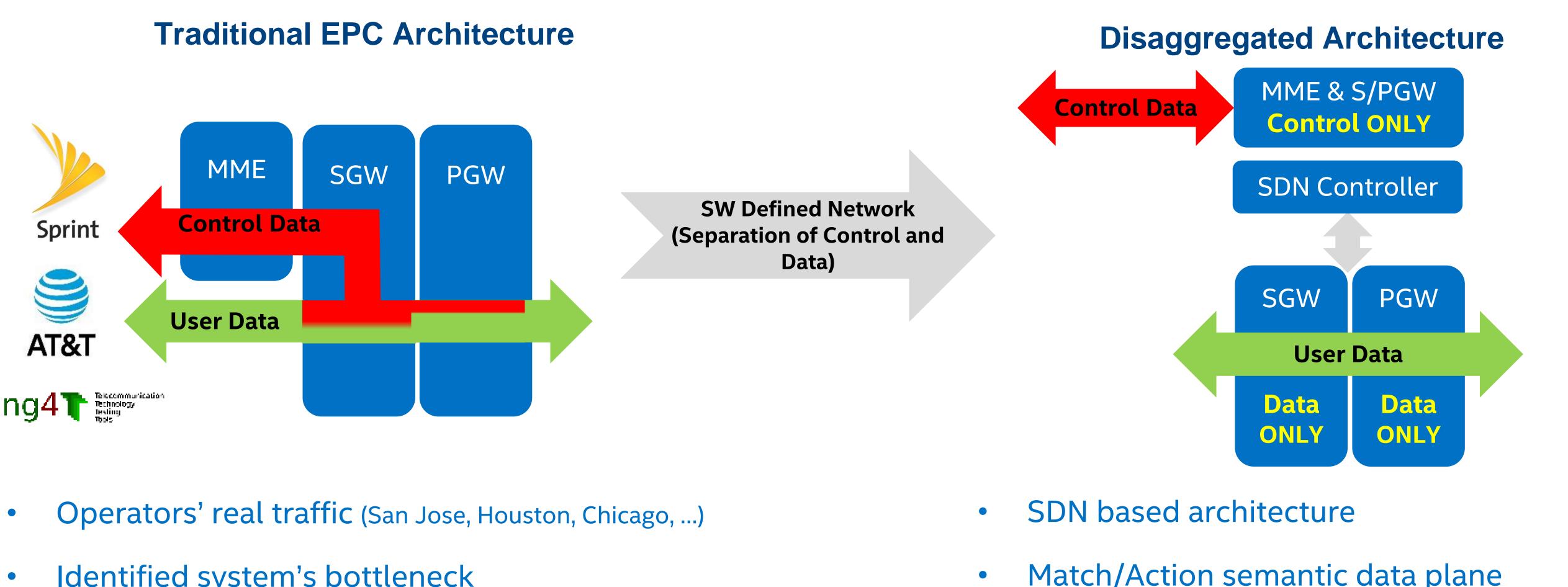

- MME, HSS, PCRF will be released later

- Investigate functionality for new usage models, e.g. Connectionless IOT, Multi-Radio Access Technologies, etc

- NGIC is not a product and will not be a product from Intel

https://gerrit.opencord.org/#/admin/projects/ngic

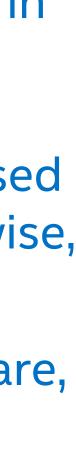

# Next Generation Infrastructure Core (NGIC)

- Identified system's bottleneck

- "Understanding Bottlenecks in Virtualizing Cellular Core Network functions", IEEE LANMAN '15

- No independent control or data scaling

"Other names and brands may be claimed as the property of others"

Intel Labs

- Match/Action semantic data plane

- Independent & scalable control & data

- Functional EPC per operator's requirements

## Functional EPC per Operator's Requirements - NGIC

https://gerrit.opencord.org/#/admin/projects/ngic

Intel Labs

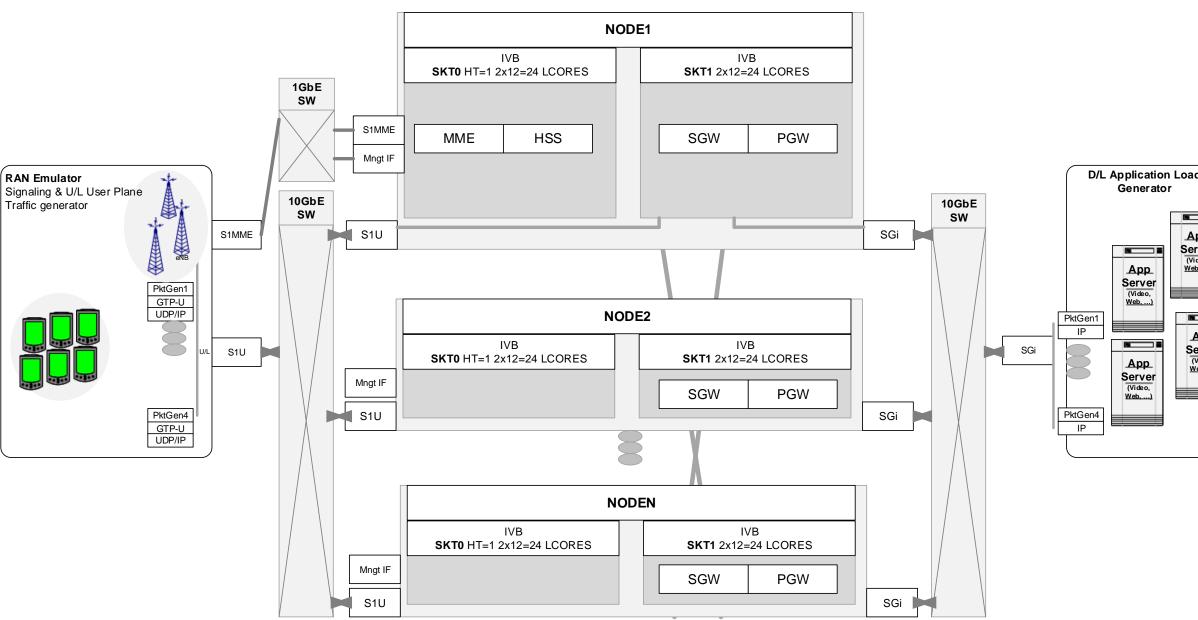

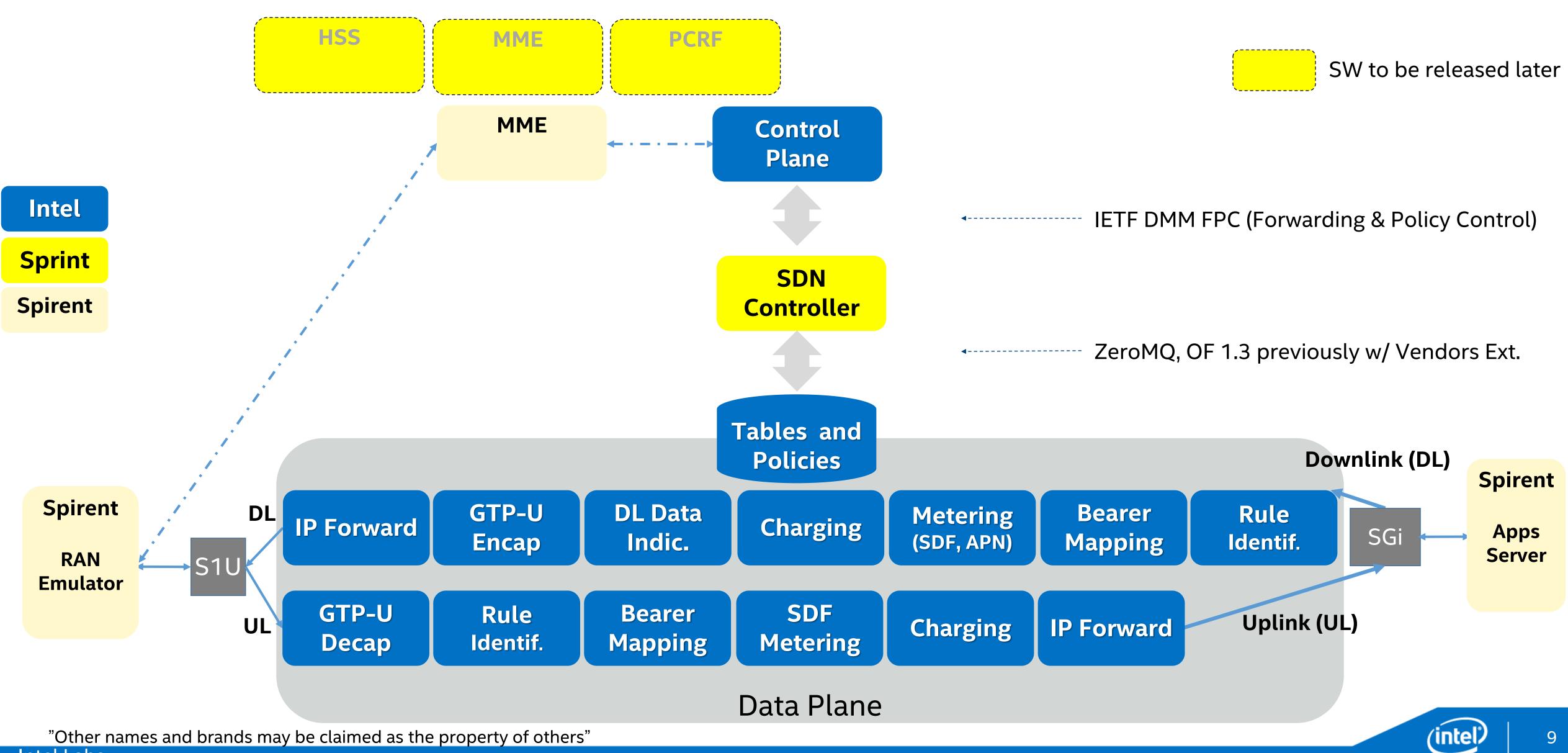

# Linear Scaling Characteristics

- 1 packet processing core

- 2.125 Million pps (50k subs)

- 1.625 Million pps (500k subs)

- 4 packet processing cores

- 8.2 Million pps (50k subs)

- 6.5 Million pps (500k subs)

All packet processing cores implement all network functions (PGW, SGW, DPI, Child Protection,

CG-NAT, static FW & SFC)

- Additional (overhead) cores for C3PO EPC Data Plane Node

- Rx Core

- Tx Core

- Load-balancing Core

- Master Core

- Interface Core

- Packet processing cores are in addition to the overhead cores

©2016 Sprint. This information is subject to Sprint policies regarding use and is the property of Sprint and/or its relevant affiliates and may contain restricted, confidential or privileged materials intended for the sole use of the intended recipient. Any review, use, distribution or disclosure is prohibited without authorization.

### From Sprint's Presentation at NFV World Congress, May 2017

11/9/2017 2:02 PM Version 1.0

# Agenda

- vEPC Background

- Next Generation Infrastructure Core (NGIC)

- CORD High Level View

- NGIC and M-CORD

- Summary / Next Steps

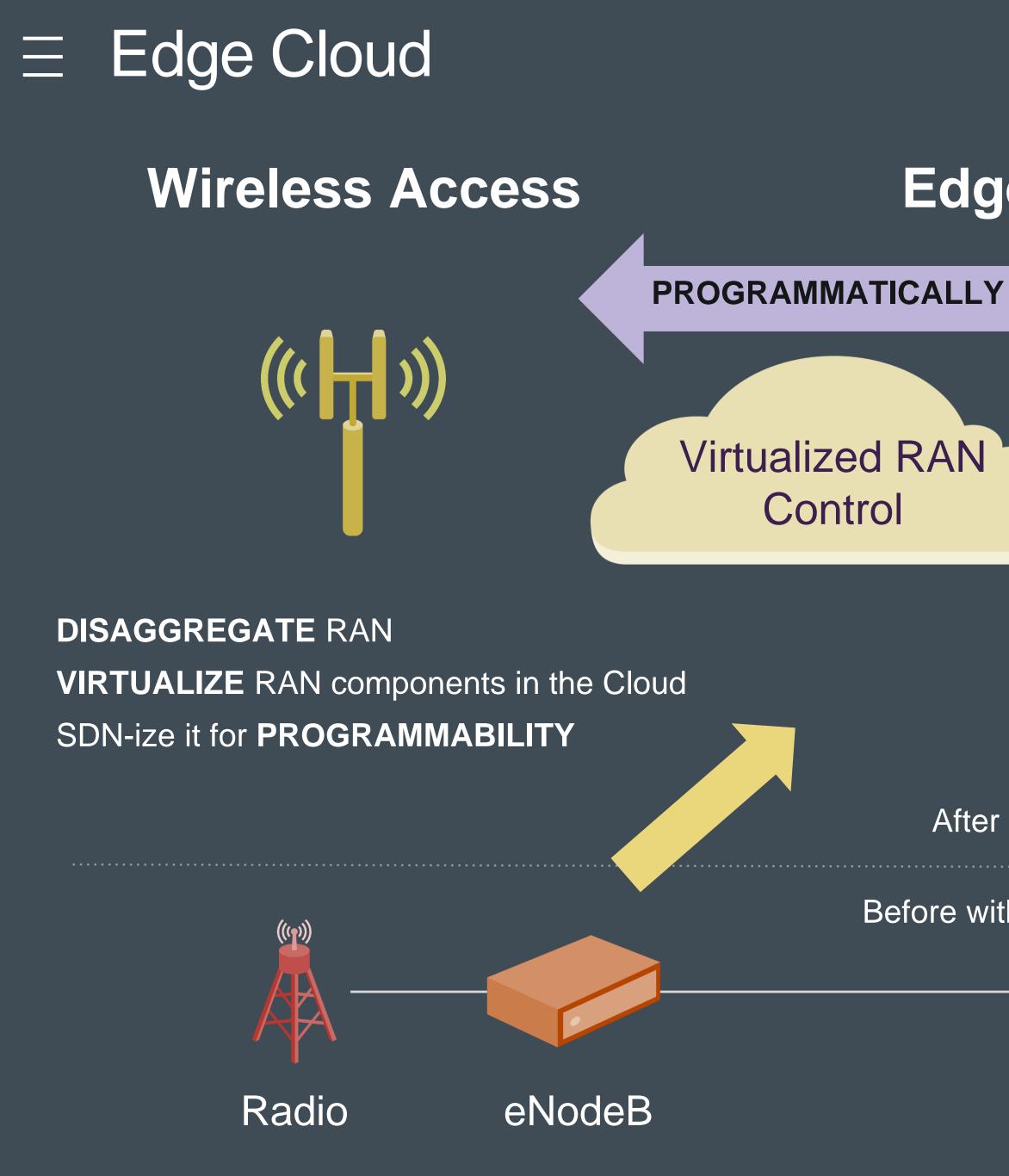

### Enabling the Programmable 5G Edge Cloud

Source: Open Networking Foundation

### $\equiv$ M-CORD: Enabling the Programmable 5G Edge Cloud

### Disaggregation

# PROGRAMMABLE 5G EDGE CLOUD

Source: Open Networking Foundation

## **¢ķķ** Programmability

Source: Open Networking Foundation

### Edge Cloud

Core

**PROGRAMMATICALLY** instantiate slices for different use cases

### Virtualized EPC

**DISAGGREGATE** Core **VIRTUALIZE** all components in the Cloud SDN-ize it for **PROGRAMMABILITY**

After with SDN & NFV

Before with dedicated hardware

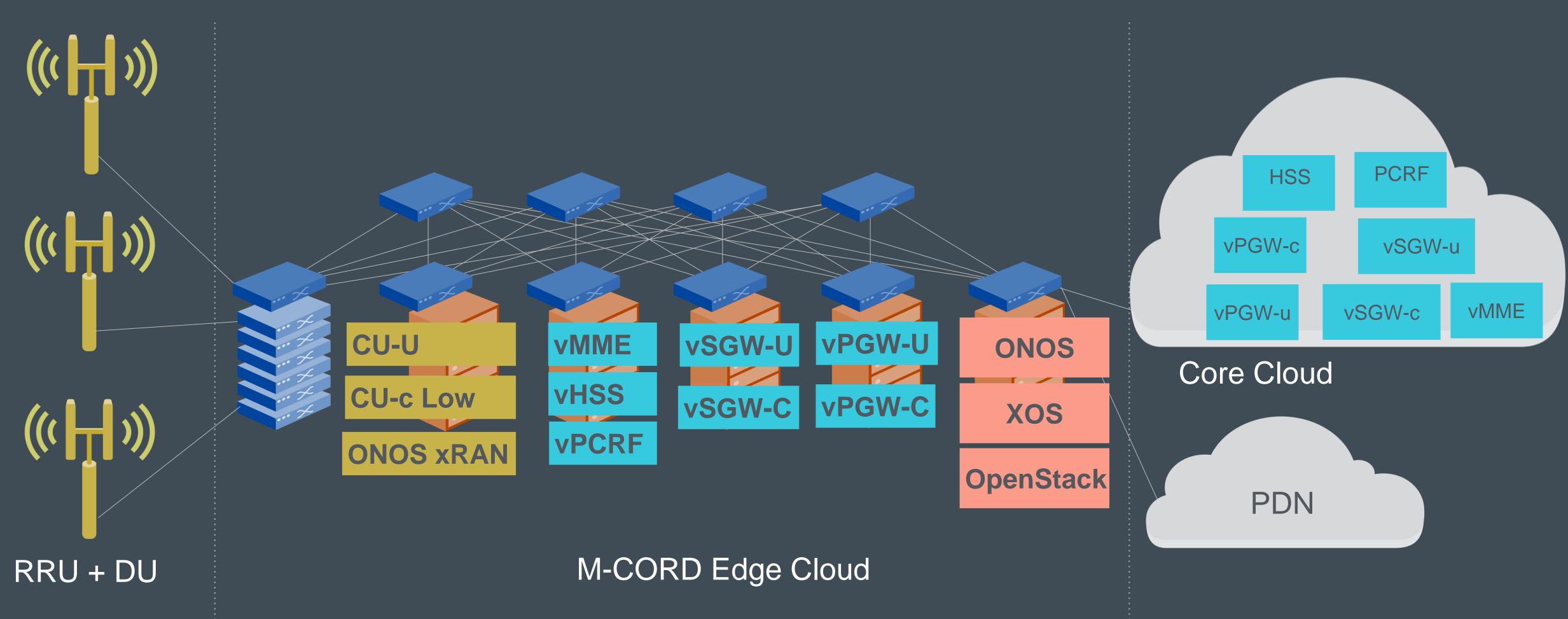

### $\equiv$ M-CORD as the Edge Cloud

Source: Open Networking Foundation

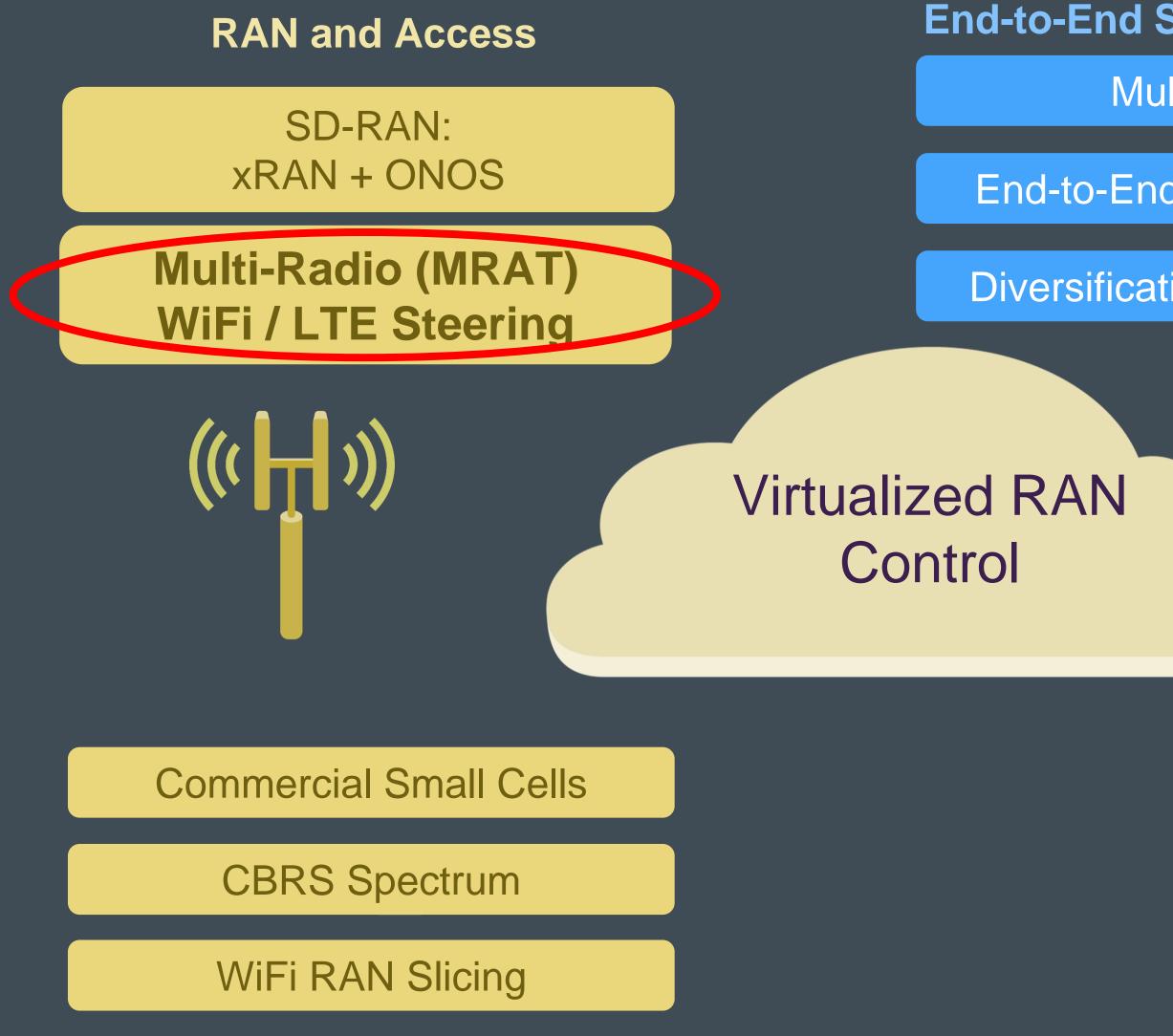

### $\equiv$ M-CORD Usage Models

Source: Open Networking Foundation

**End-to-End Solution PoCs & Capabilities**

Multi-Access CORD

End-to-End Network Slice Stitching

**Diversification of Hardware Choices**

### Virtualized EPC

Mobile Core

**Open Source EPC**

Infrastructure Acceleration

# Agenda

- vEPC Background

- Next Generation Infrastructure Core (NGIC)

- CORD High Level View

- NGIC and M-CORD

- Summary / Next Steps

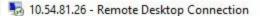

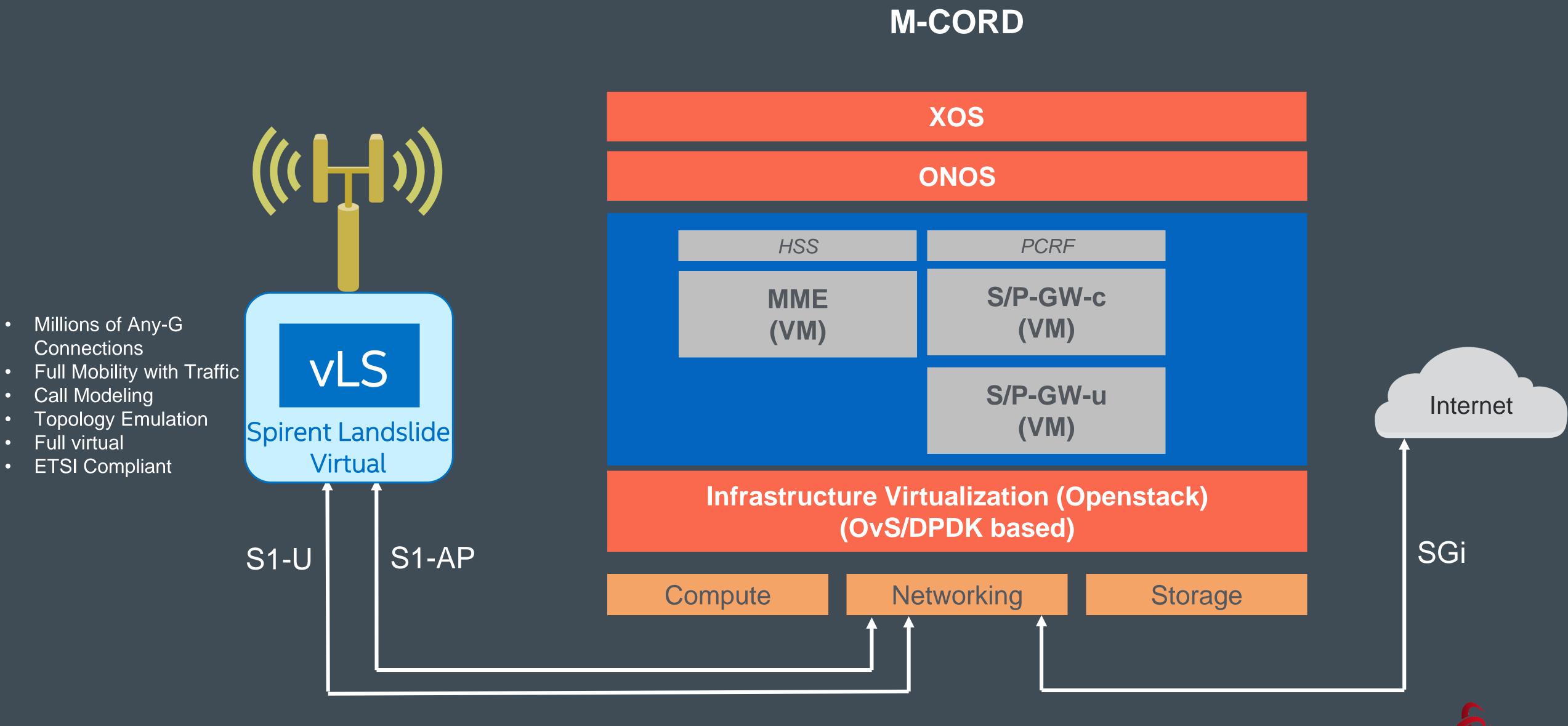

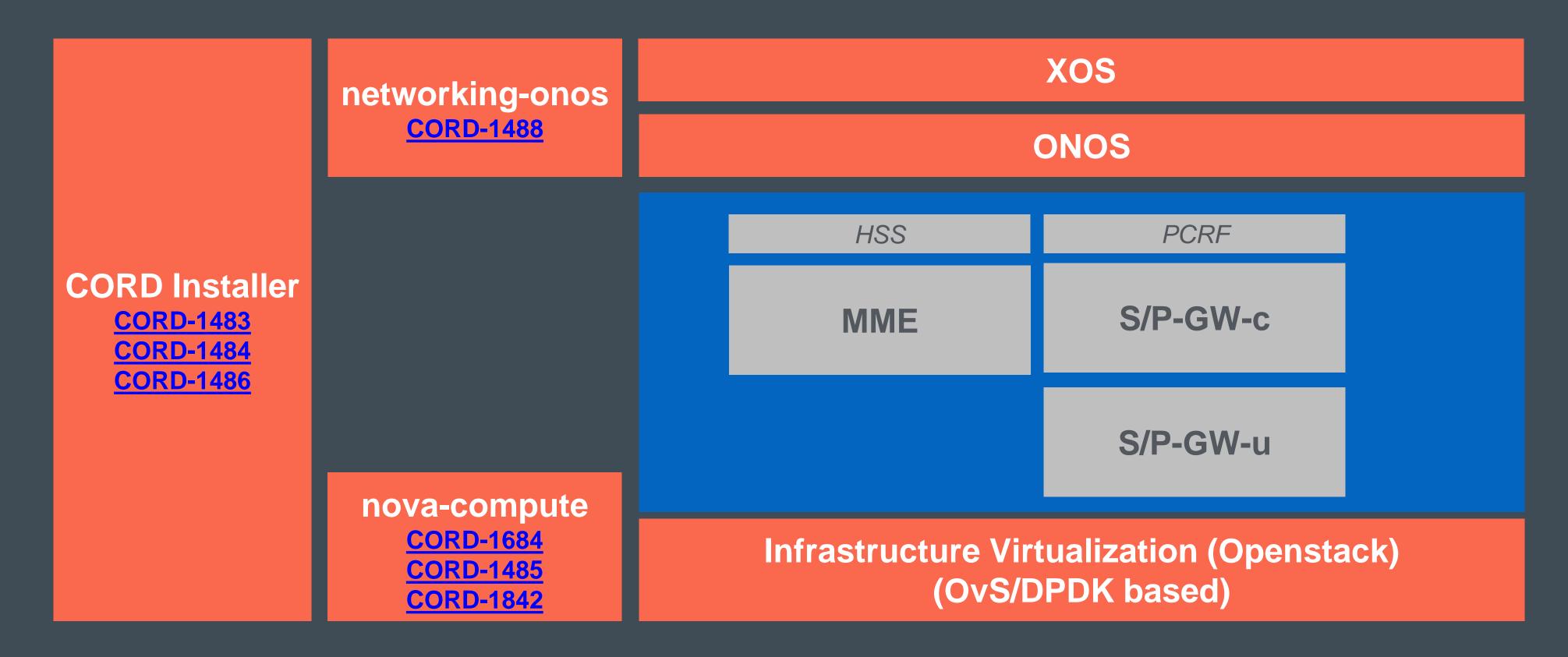

# NGIC (VEPC) & M-CORD

https://gerrit.opencord.org/#/admin/projects/ngic

### $\equiv$ NGIC & M-CORD

Source: Open Networking Foundation

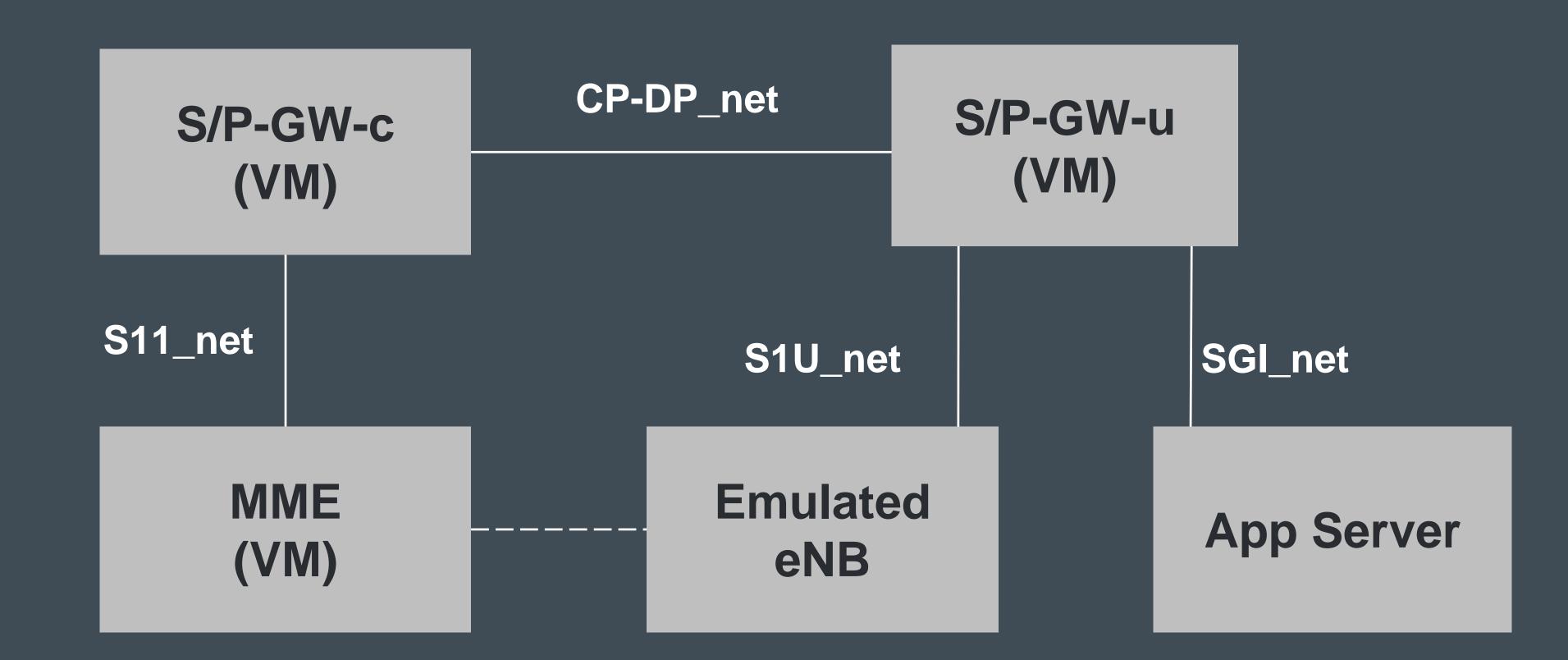

### $\equiv$ LOGICAL NETWORK CONNECTIVITY IN CORD

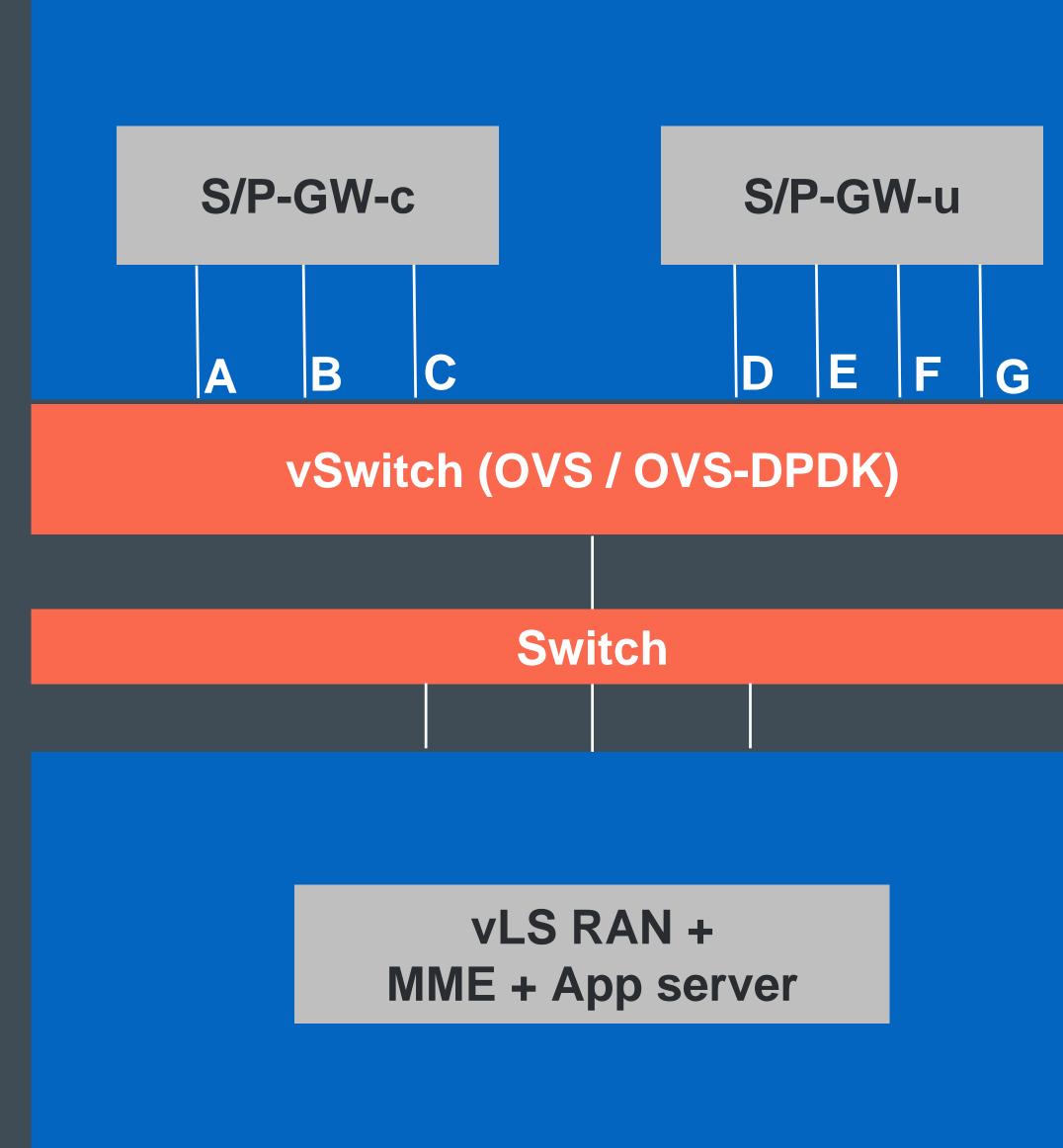

### $\equiv$ **PHYSICAL NETWORK CONNECTIVITY**

### Legend:

A,D management B,E CP-DP\_net S11\_net С S1U\_net F SGI\_net G

MANAGEMENT PRIVATE ACCESS\_AGENT ACCESS\_AGENT ACCESS\_AGENT

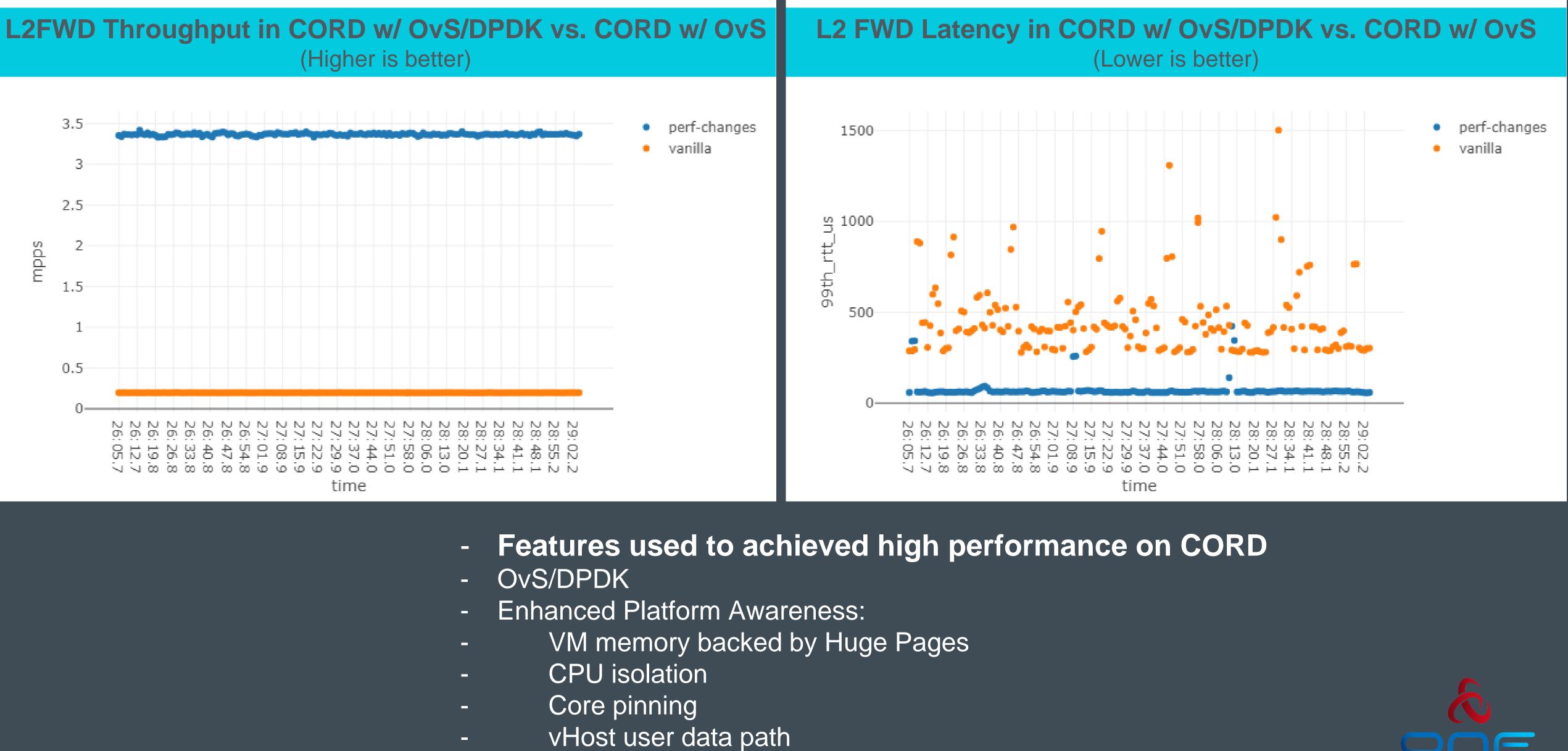

### $\equiv$ M-CORD using OvS/DPDK and Enhanced Platform Awareness

CORD-1483: Configure Nova with DPDK-enabled flavors CORD-1484: Add nova config options to juju\_config.yml CORD-1485: Install OVS-DPDK through nova-compute charm CORD-1486: Set kernel commandline parameters for compute nodes CORD-1488: Add VIF details to handle VHOST\_USER port type. CORD-1842: Replace default QEMU with patched QEMU 2.7.0 for correct functioning of VHOST\_USER

- CORD-1684: Backport libvirt driver changes, to enable memAccess=shared tag required for correct functioning of VHOST\_USER

### $\equiv$ M-CORD using OvS/DPDK and Enhanced Platform Awareness

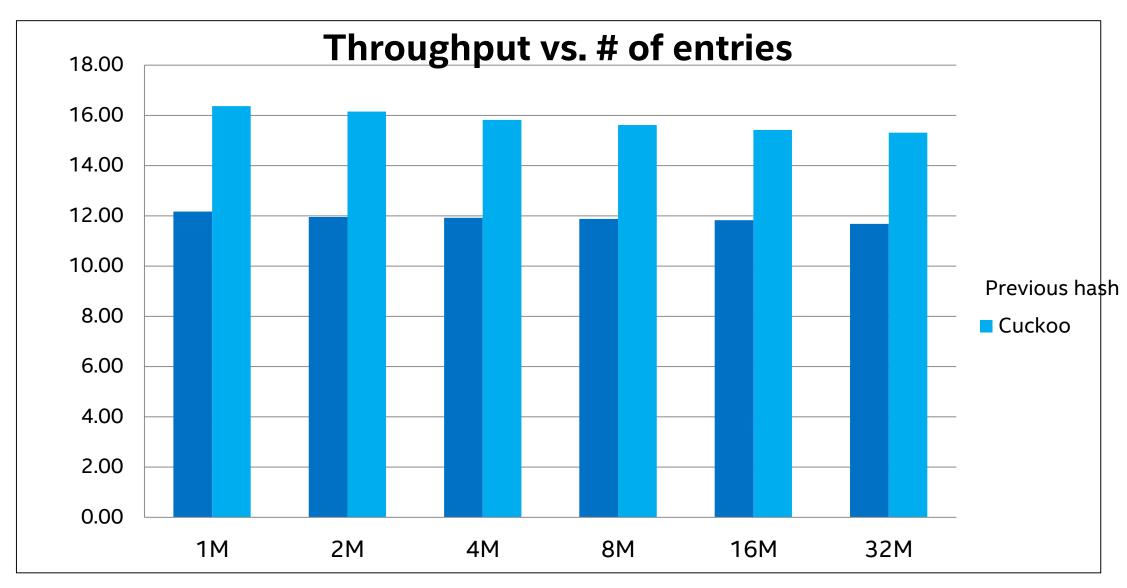

### (Higher is better)

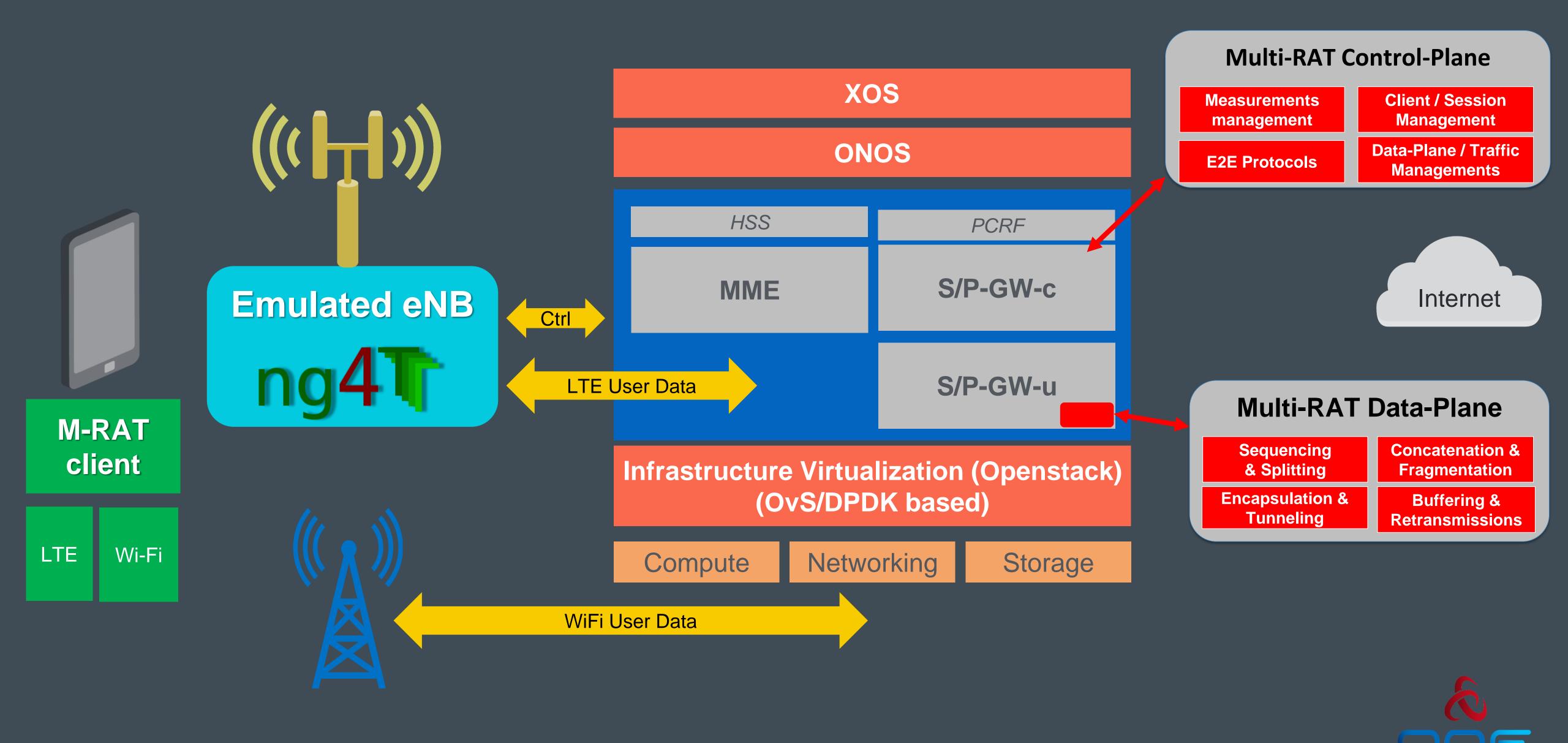

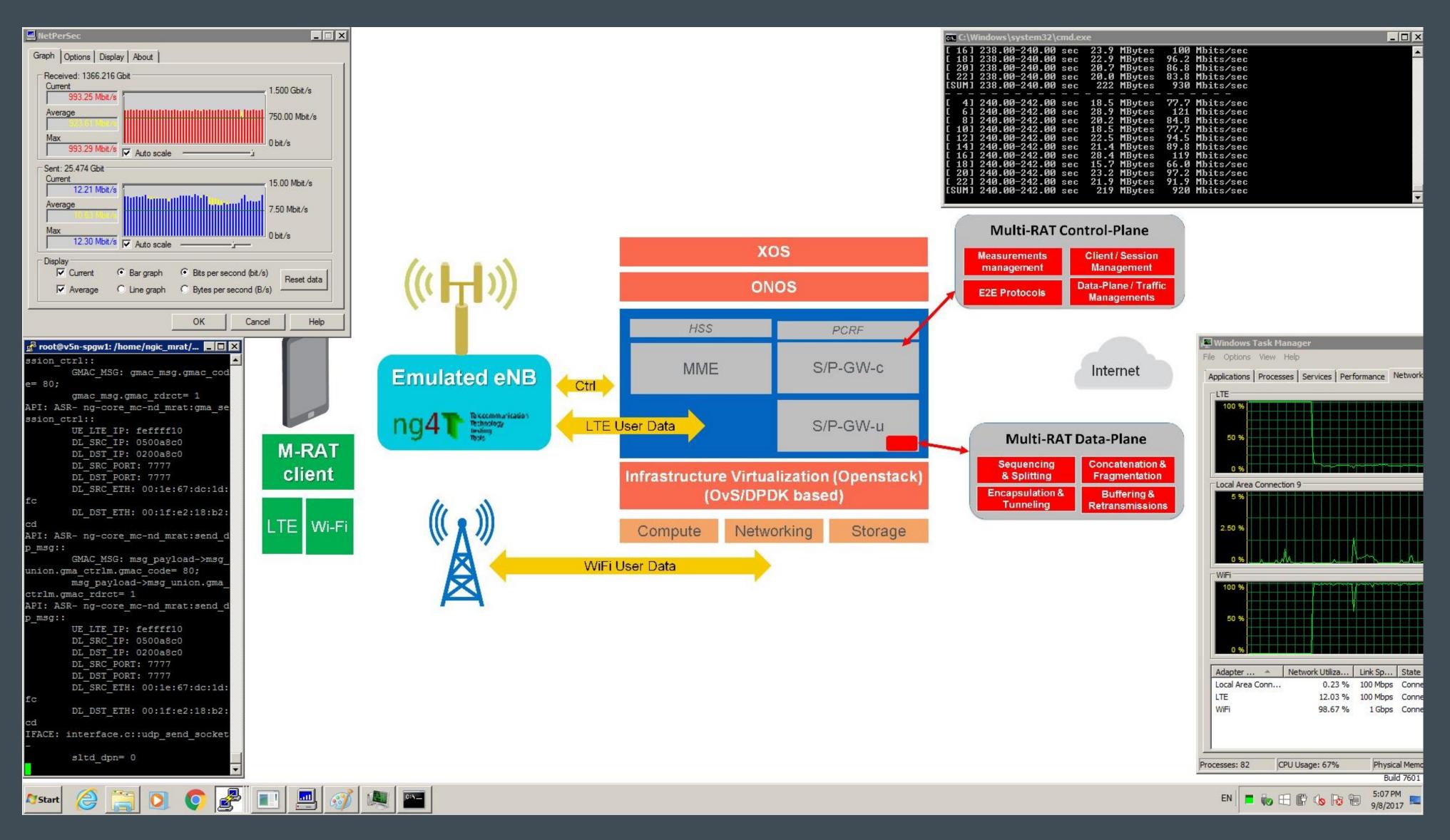

### $\equiv$ Modules: vEPC & M-RAT (1/2)

"Other names and brands may be claimed as the property of others"

### $\equiv$ Modules: vEPC & M-RAT (2/2)

# Agenda

- vEPC Background

- Next Generation Infrastructure Core (NGIC)

- CORD High Level View

- NGIC and M-CORD

- Summary / Next Steps

# Summary / Next Steps

- NGIC is a functional, DPDK based, EPC operating in bare-metal, VMs, or containers and orchestrated in M-CORD

- Additional EPC components, MME, HSS, PCRF, will be made available to CORD over time

## **NGIC Hands-on Tutorial Next**

### **Prerequisites for Hands-on Tutorial**

- Install Docker (1.13 or higher) and Docker Compose

- Docker images for NGIC control, data plane and traffic generation docker pull ngiccorddemo/ngic-cp docker pull ngiccorddemo/ngic-dp docker pull ngiccorddemo/ngic-traffic

- Demo folder

git clone https://github.com/ngiccorddemo/cordbuild2017.git

Intel Labs

Intel Confidential – Internal Use Only

experience what's inside<sup>™</sup>

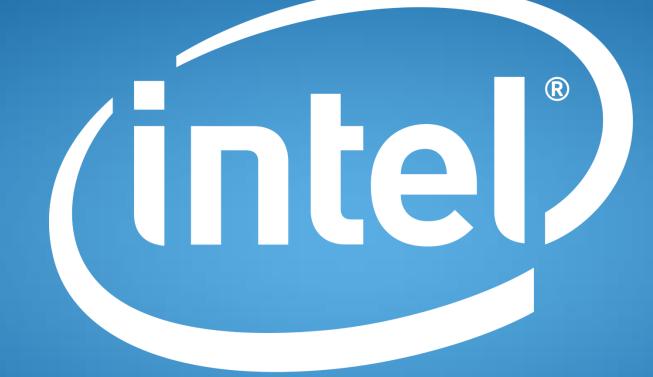

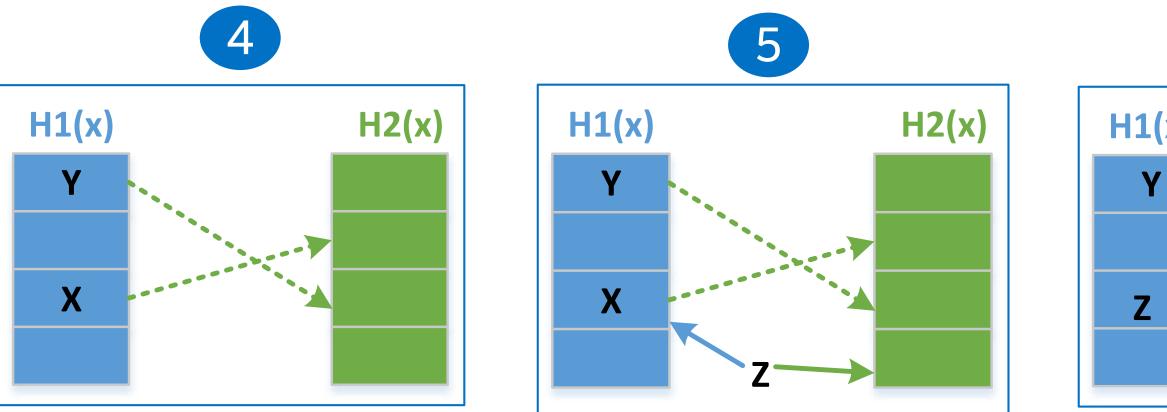

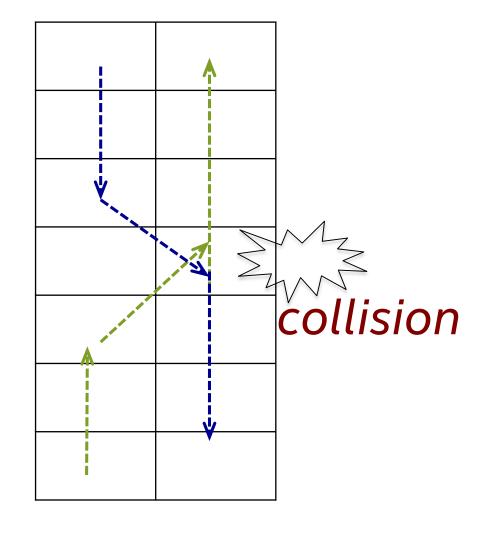

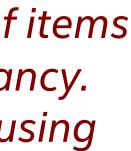

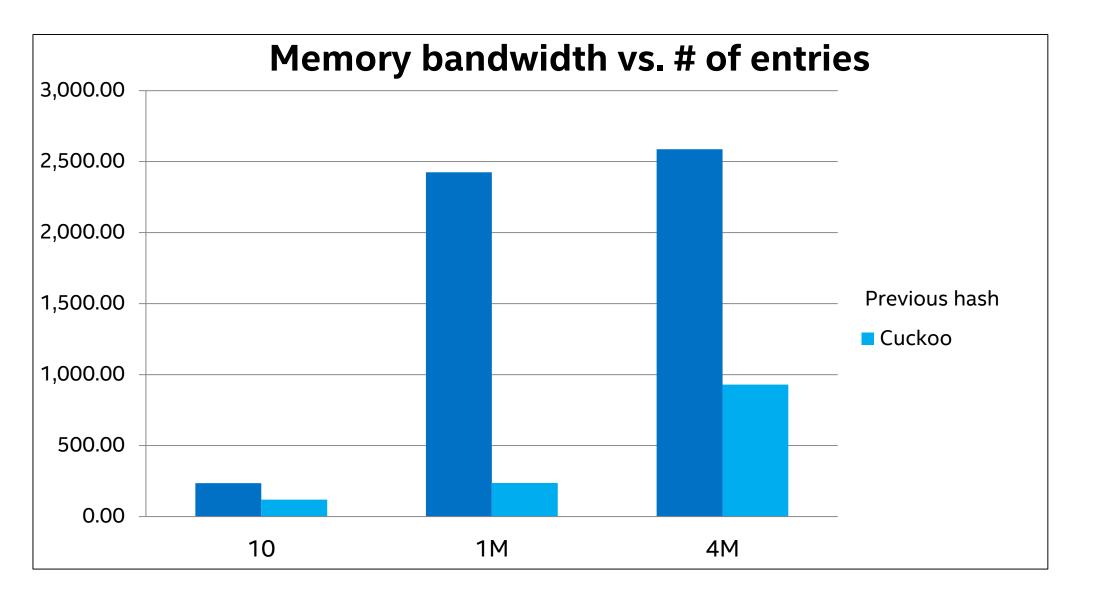

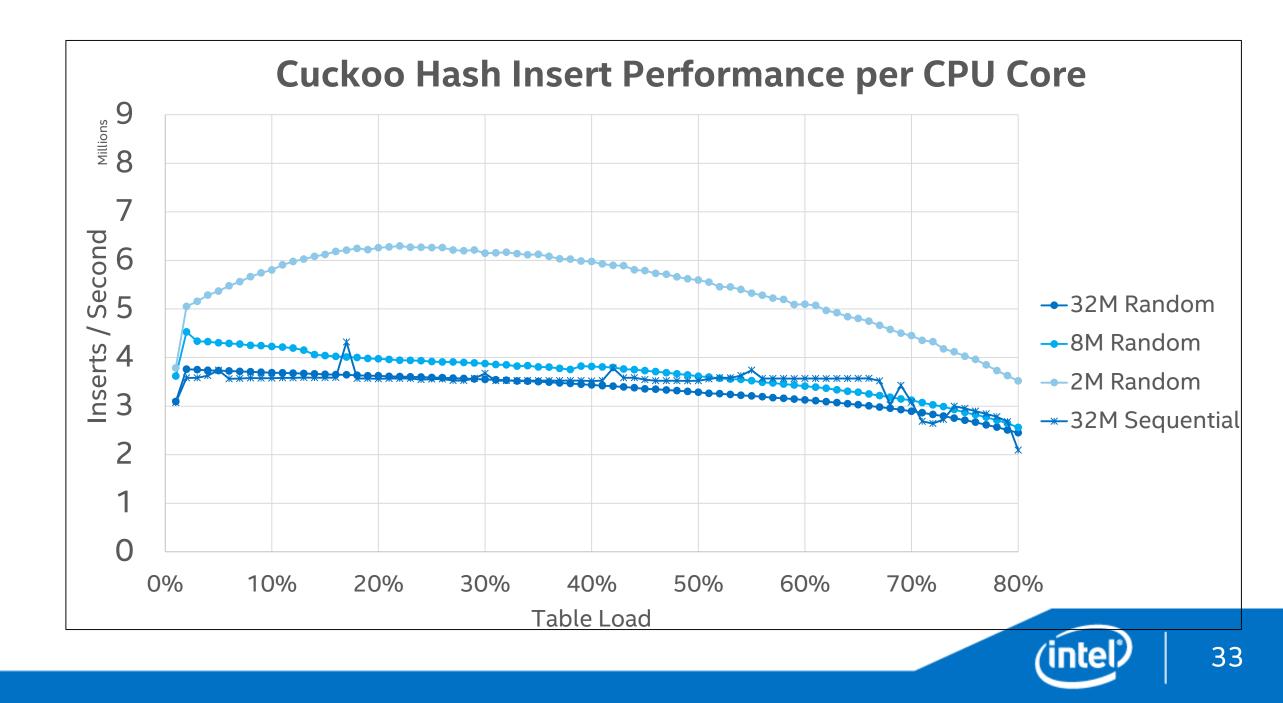

## Efficient MATCH/Action Semantic Data Plane (1/2)

### Match/Action : Optimized Table Lookup with Cuckoo Hashing<sup>[Pagh 01]</sup>

### Intel Labs

"Scalable, High Performance Ethernet Forwarding with CuckooSwitch", Dong Zhu, Bin Fan, Dave Anderson (CMU), Michael Kaminsky (Intel)

**One** Insert **may move a lot of items** especially at high table occupancy. Optimal multi-writer insertion using Intel<sup>®</sup> TSX

## Efficient MATCH/Action Semantic Data Plane (2/2)

Intel Labs

### $\equiv$ Modules: vEPC & M-RAT (2/2)