Sponsored By

#### Silicon One - Multiple roles

Guy Caspary Engineering Director Cisco

#### A single silicon architecture for all market segments

# The problem

**CISCO**

- Silicon devices address two different use cases: routers and switches.

- Routers are highly programmable, with deep buffers and large scale.

- Switches are high bandwidth with low power consumption.

The industry diverged into two markets: each defined by unique architecture, systems and software.

# A brief history

- Work on Silicon One started six year ago

- We identified that programmability is a must

- Features:

- Faster SW development is faster than silicon development

- Longer features are added pre- and post- silicon

- Safer bugs can be fixed post-silicon

- Broad market applicability

- A fixed function device must support the super-set of all functions

- Maintainability

### ılıılı cısco

3

# Why P4

- Several tasks were performed in parallel:

- Coding of high level application to cover all markets

- Architecture design

- Development tools (e.g. compiler, debugger)

- Started with C but found out it is too general.

- Application paradigm was naturally match/process.

- Decided to adopt P4 as base.

# NPU architecture

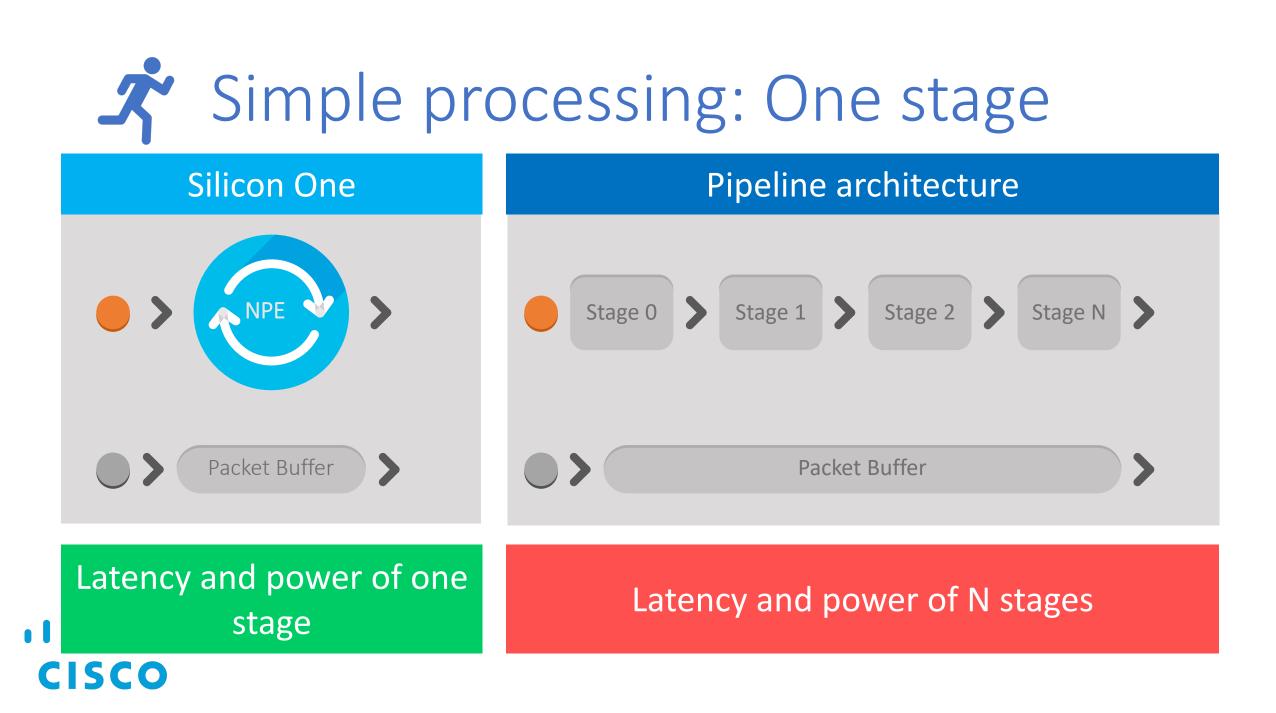

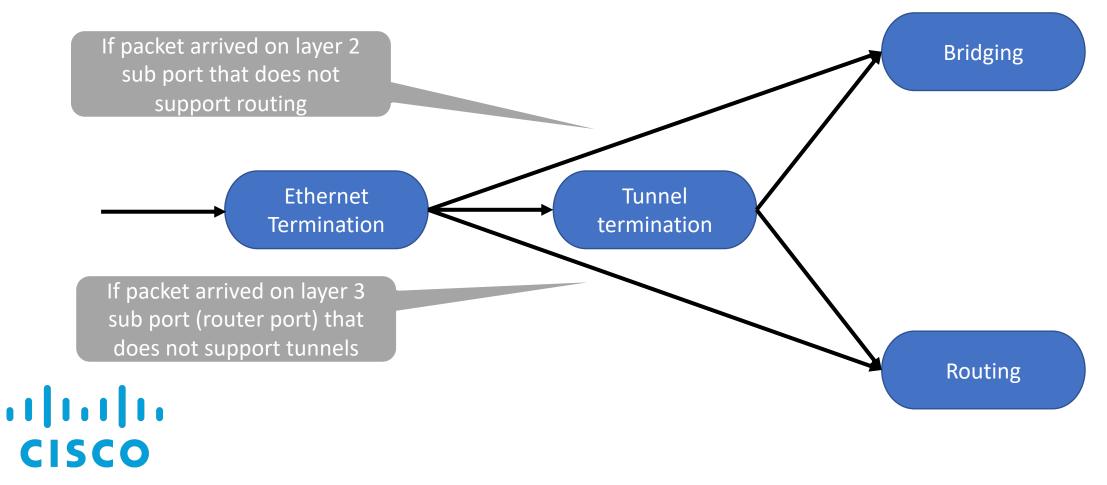

NPU contains an array of processing engines Run-to-complete P4 programmable

.....

**CISCO**

One code image covers all markets

Different flows execute different parts of the application Architecture allows for a different number of processors Performance and feature scalability

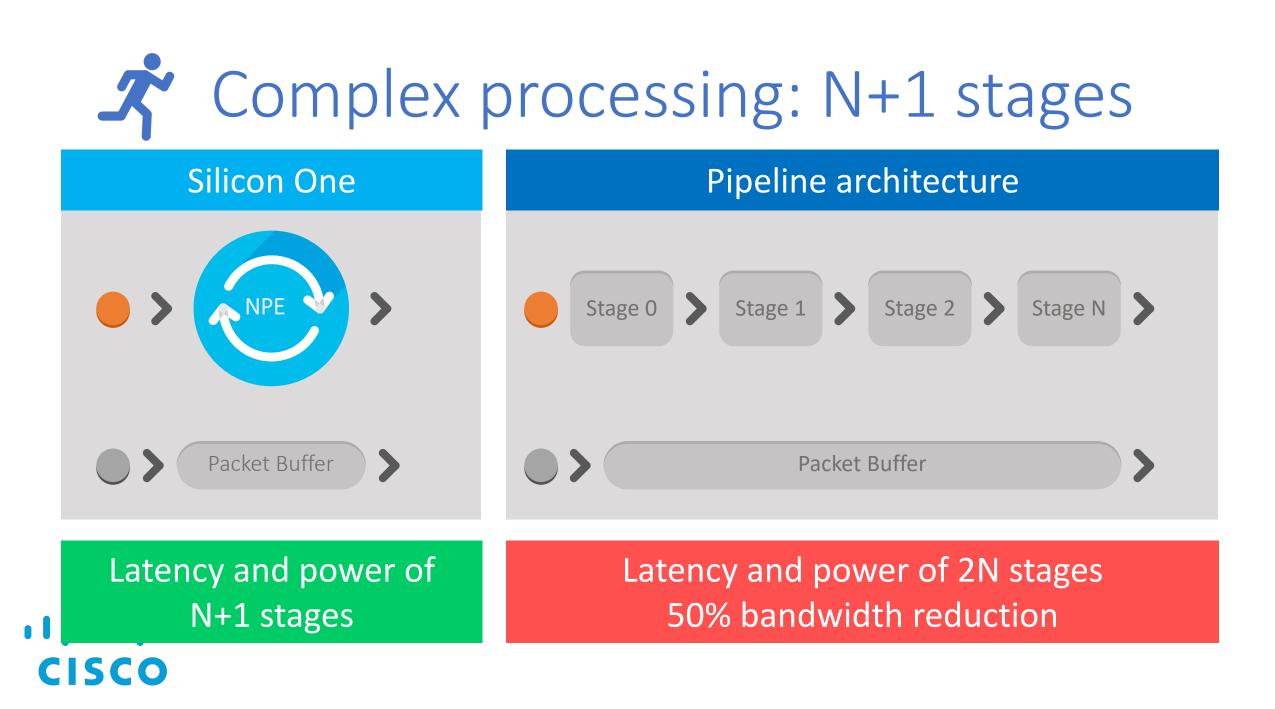

# Why run to complete?

- For each packet we spend the "exact" amount of cycles, latency and power required

- Very complex but low bandwidth flows (e.g. control packets) have negligible impact on performance

Allows for natural and efficient coding

- The first architecture that serves several different market segments service provider and web-scale.

- Elevating routing silicon performance to the same level as switching silicon performance (bandwidth and power).

- Allows for future product lines to have a consistent silicon architecture.

- ONE experience across the entire network, across all network functions and covering all form factors.

- Significantly reduce OpEx: network engineers save time on testing functionality, qualifying new hardware, and deploying new services with greater consistency and faster time-to-market.

# ılıılı cısco

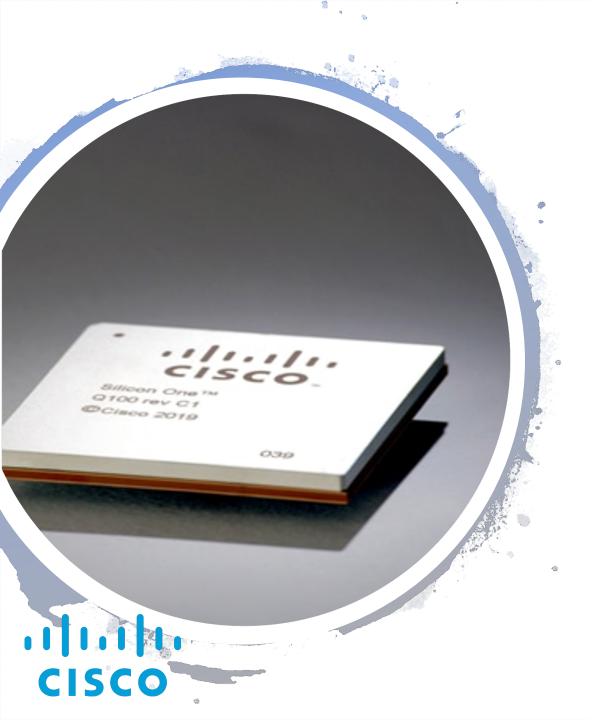

# Cisco Silicon One Q100

- The first device in this architecture

- The first routing silicon to break through the 10Tbps benchmark for network bandwidth, without compromising carrier-class capabilities, e.g., feature richness, large queue set, deep buffers, large NPU tables, and advanced programmability.

- Demonstrates many architectural advantages:

- Supports a fixed switch or router with 10.8T worth of network ports up to large non-blocking distributed routers with Petabit scales.

- All with non-blocking performance, deep buffering with rich QoS, and programmable forwarding.

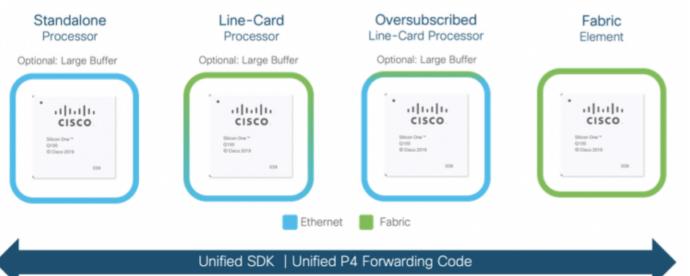

# Cisco Silicon One Q100 – cont.

- A single device may be used as standalone network processor (optional deep buffers), line card network processor (optional deep buffers) and fabric element in a distributed router.

- All accomplished with a common and unified P4 forwarding code and SDK.

# ·IIIII CISCO

# Cisco 8000 series routers

- Powered by Cisco Silicon One ASICs supporting full routing functionality with a single ASIC.

- Platforms scale from 10.8 Tbps to 260 Tbps.

- Common architecture and designs across modular and fixed routers provide topological regularity, scalability, consistent features and operational simplicity.

### Cisco 8200 Series

3

CISCO

- Uses the Cisco Silicon One Q100 to deliver full routing functionality with a single ASIC per router.

- The architecture supports large forwarding tables, deep buffers, flexible packet operations, and enhanced programmability.

- Two fixed 10.8Tb/s platforms:

- The Cisco 8201 is a 1RU fixed configuration with 24x400GbE and 12x100GbE ports

- The Cisco 8202 is a 2RU fixed configuration with 12x400GbE and 60x100GbE ports

### Cisco 8800 Series

3

High bandwidth via modular chassis with a redundant control plane and switch fabric:

- The Cisco Router 8808 is an 8-slot, 115.2 Tb/s, 16RU chassis

- The Cisco Router 8812 is a 12-slot, 172.8 Tb/s, 21RU chassis

- The Cisco Router 8818 is an 18-slot, 259.2 Tb/s, 33RU chassis

\*Total bandwidth is based on Silicon One Q100; infrastructure provides for more. Stay tuned ...

# Programmability in action: Pre/Post silicon validation

- A dedicated P4 application for silicon verification and validation

- A non-standard injected packet contains commands for the device:

- Path through device

- Resources to exercise:

- Lookups

- Counter increments

- more

| . |     |   | ) |

|---|-----|---|---|

| C | ISC | 0 |   |

| / |   |  |

|---|---|--|

| ( | - |  |

|   |   |  |

|   |   |  |

|   |   |  |

|   |   |  |

# Programmability in action: power measurement

- Fast bring-up of power testing application defined by customer:

- Ethernet packets

- Specific flow through ports

- Specific database lookups

- Prototype in 2 hours

- Debug and testing in 2 days

- Delivered a week after request ...

- Shipping and customs clearance 7 days

## ılıılı cısco

**CISCO** Silicon One

Sponsored By

### **Thank You**

#### Contact: Guy Caspary <gcaspary@cisco.com>

Sponsored By

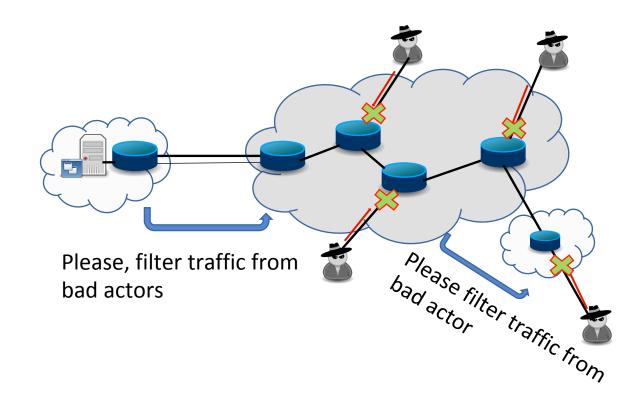

# Security Stability and Transparency: is P4 the answer?

Dr. Paola Grosso Associate Professor "Multiscale Networked Systems" University of Amsterdam – The Netherlands

mns-research.nl

# Science usecases

Photo source: SKA organisation

Radio astronomy (SKA)

High energy physics (LHC)

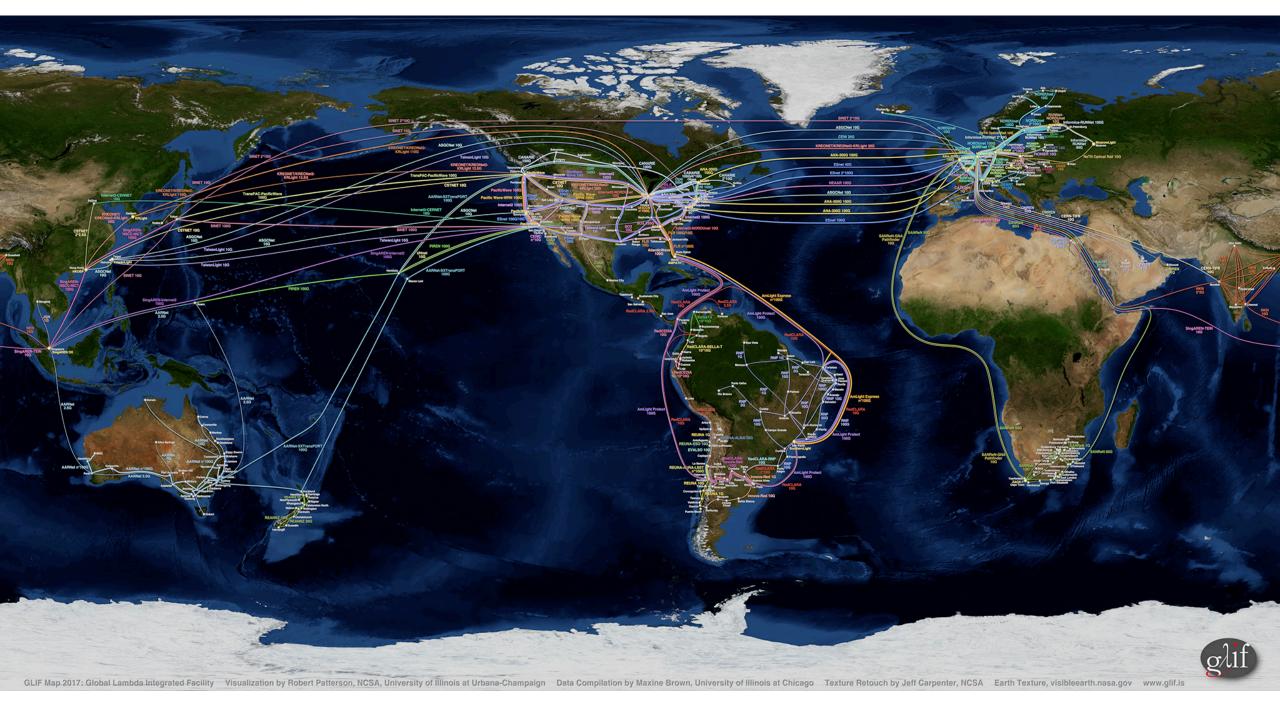

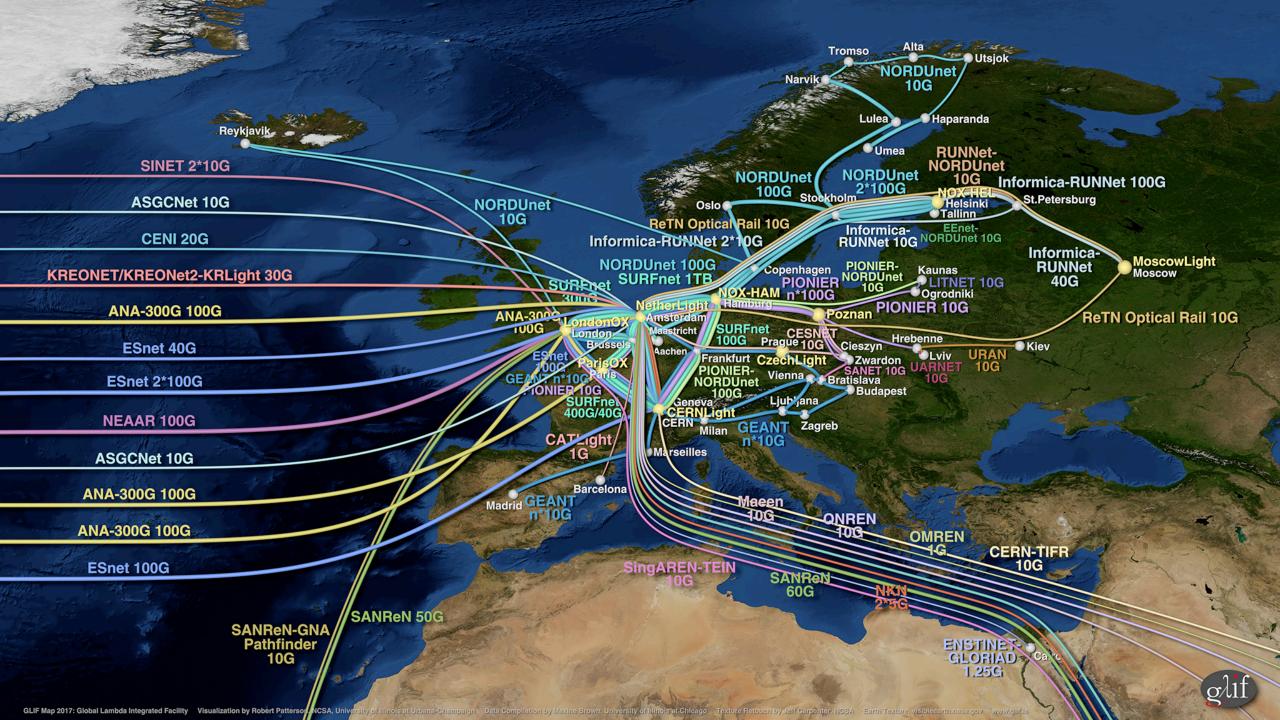

Science data is moving around the world

Photo source: LSST/NSF/AURA Radio astronomy (LSST)

# Societal usecases

Photo source: Genetic Literacy Project

Personalized medicine (EPI)

Photo source: DL4LD project

Logistics (DL4LD)

#### Personal data is shared by many parties.

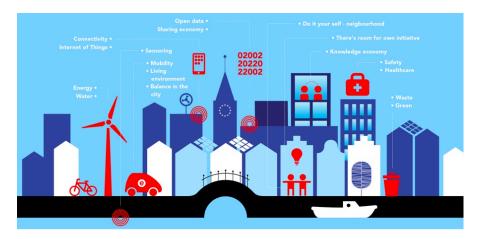

Smart cities (AMDeX)

Photo source: AMS Economic Board

Multiscale Networked Systems

# How can we provide security, stability and transparency in the networks of the Future?

Not just from the perspective of network operators but also for end users!

# Why P4?

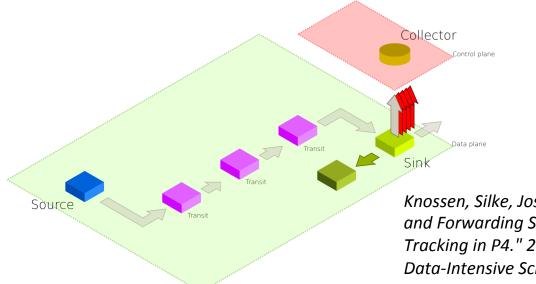

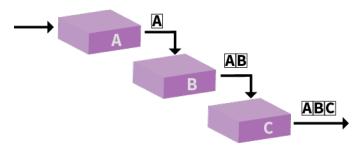

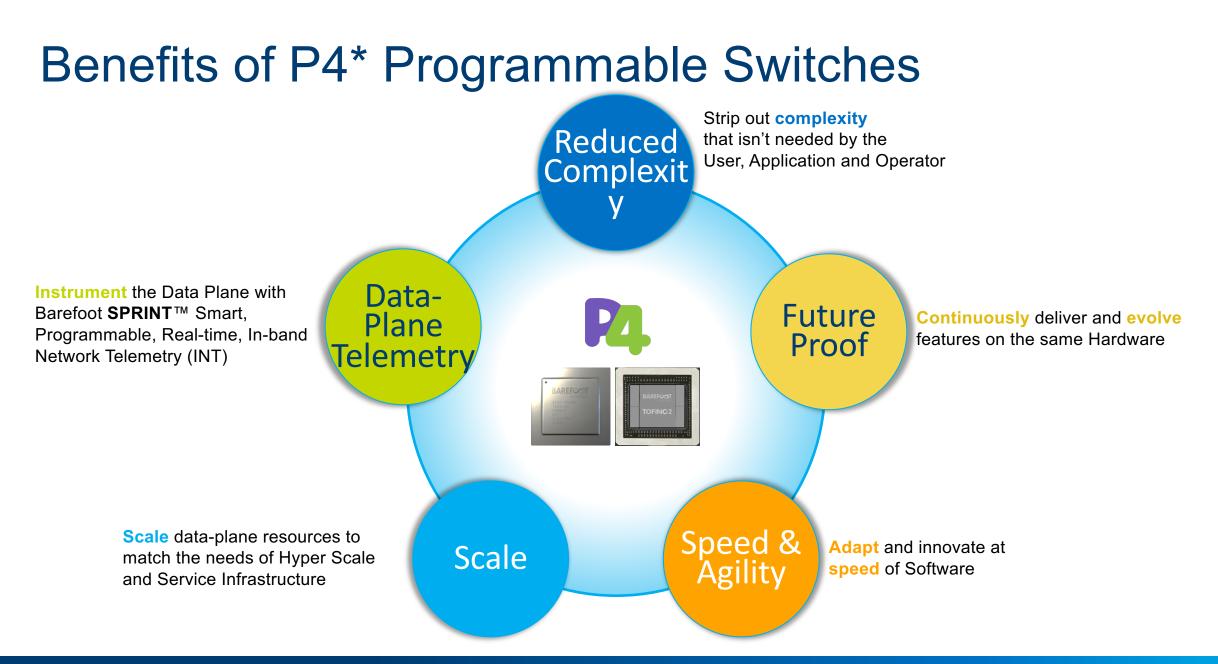

Per packet processing in the dataplane provides advantages compared to out-of-band approaches for fine grained telemetry. No need for summarization and a wealth of information that is usable in many contexts.

- <u>Transparency goal</u>:

- From telemetry we acquire insights in what is happening in the network, eg the path taken by flows.

- <u>Security goal</u>:

- From telemetry follows the possibility to identify attacks and feed intrusion detection systems (see SARnet project).

- <u>Stability goal:</u>

- From telemetry follows you can identify bottlenecks and buffers filling up along the path, eg the amount of data in queues leveraging time stamping.

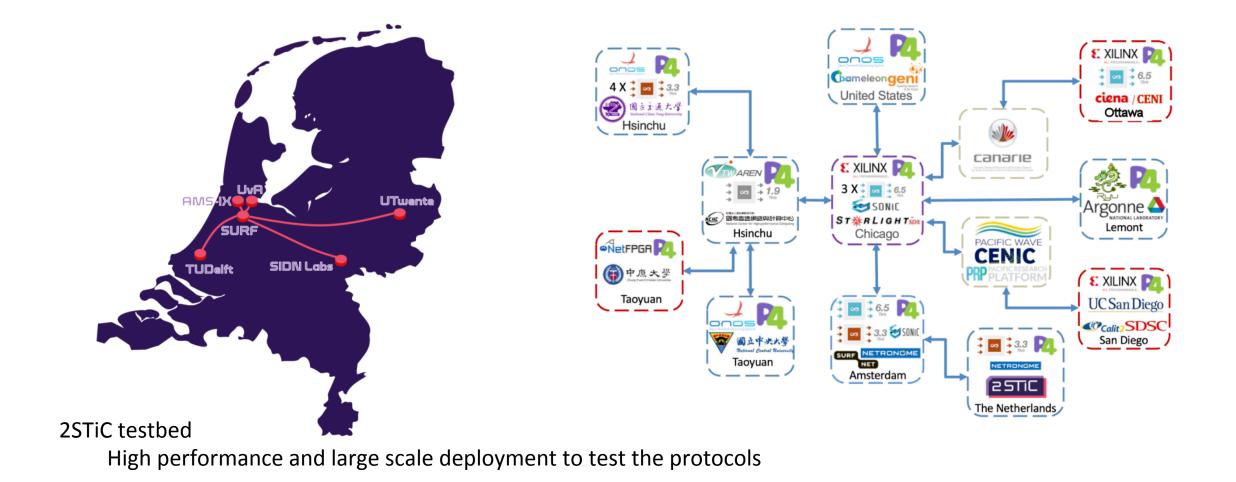

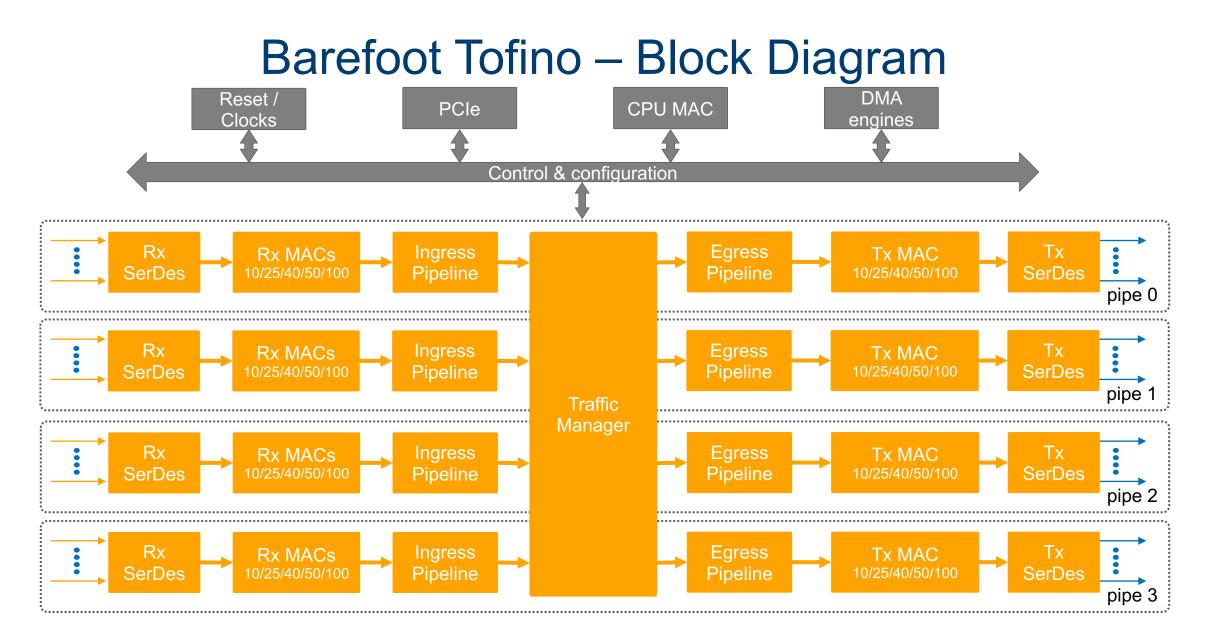

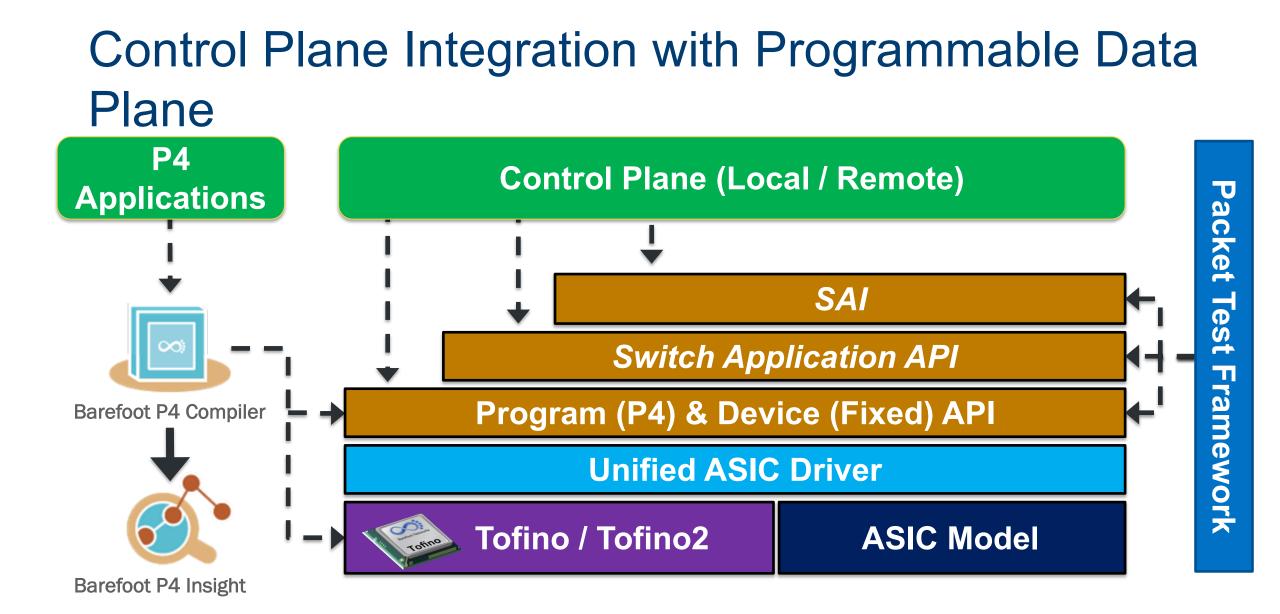

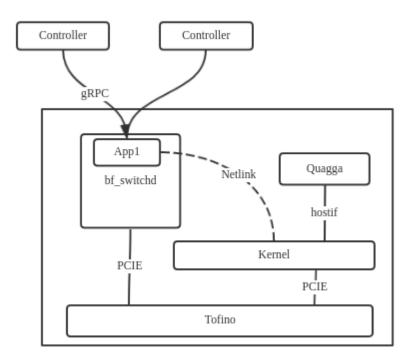

# How we use P4?

Use of the software switch and compilers from p4.org for our initial research and then moved to hardware (\*).

- Barefoot switches give us better performance switching capabilities

- Smart NICS allow us to bring the P4 capabilities all the way to host

- (\*) Still very useful in educational settings for students labs.

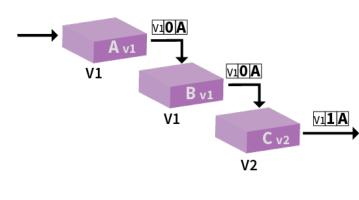

# Telemetry

Multiscale Networked Systems

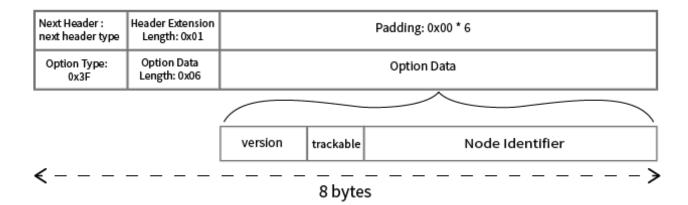

Knossen, Silke, Joseph Hill, and Paola Grosso. "Hop Recording and Forwarding State Logging: Two Implementations for Path Tracking in P4." 2019 IEEE/ACM Innovating the Network for Data-Intensive Science (INDIS). IEEE, 2019.

| Next Header :<br>next header type | Header Extension<br>Length: 0x02 | Padding: 0x00 * 6            |

|-----------------------------------|----------------------------------|------------------------------|

| Option Type:<br>0x3F              | Option Data<br>Length: 0x06      | Option Data: Node Identifier |

| Option Type:<br>0x3F              | Option Data<br>Length: 0x06      | Option Data: Node Identifier |

| <pre></pre>                       |                                  |                              |

8 bytes

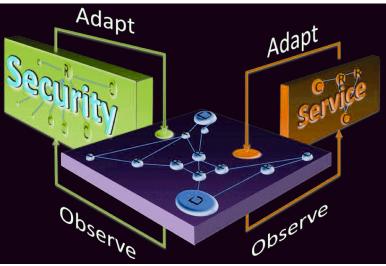

# Security

#### Adapting for autonomous response (ML learning)

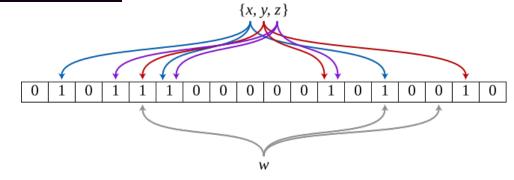

Bloom filters in P4

*Hill, Joseph, Mitchel Aloserij, and Paola Grosso. "Tracking network flows with P4."*

2018 IEEE/ACM Innovating the Network for Data-Intensive Science (INDIS). IEEE, 2018.

2576

SECURITY, STABILITY AND TRANSPARENCY OF INTER-NETWORK COMMUNICATIONS

Sponsored By

Thank You... ... and thanks to Silke Knossen, Mitchell Aloserij and Joseph Hill (from UvA)

p.grosso@uva.nl

2stic.nl mns-research.nl

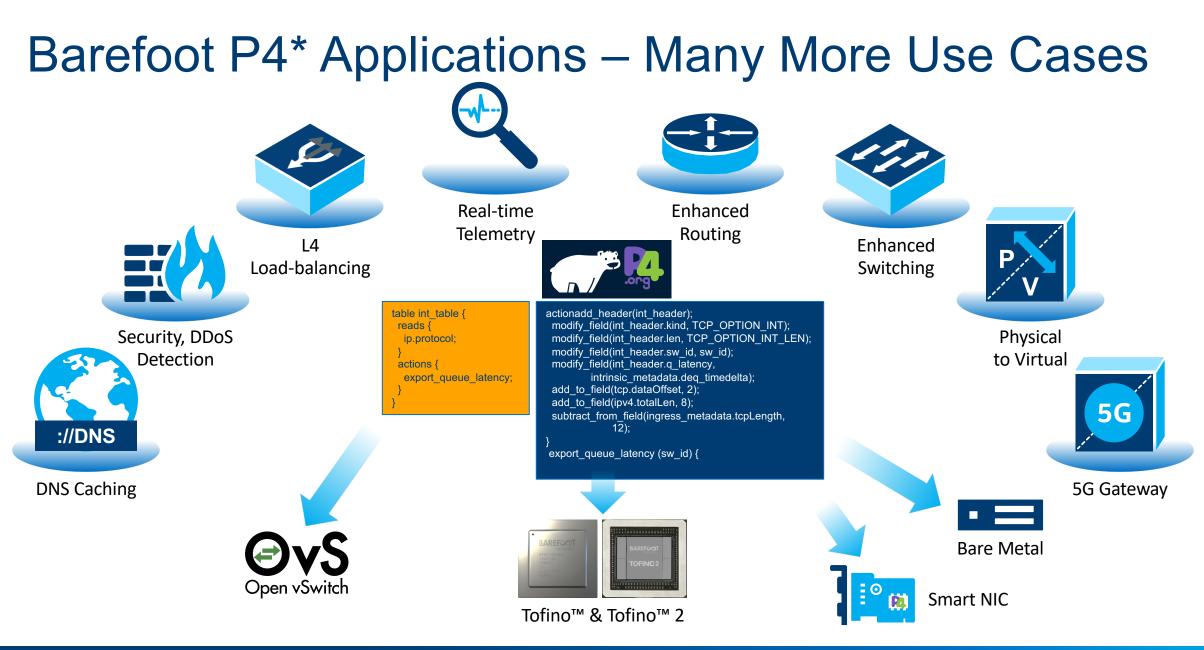

# P4-Programmable Data Plane Use-cases

Arkadiy Shapiro, Product Line Manager, Software

Barefoot Division, Connectivity Group, Intel

Arkadiy.Shapiro@intel.com

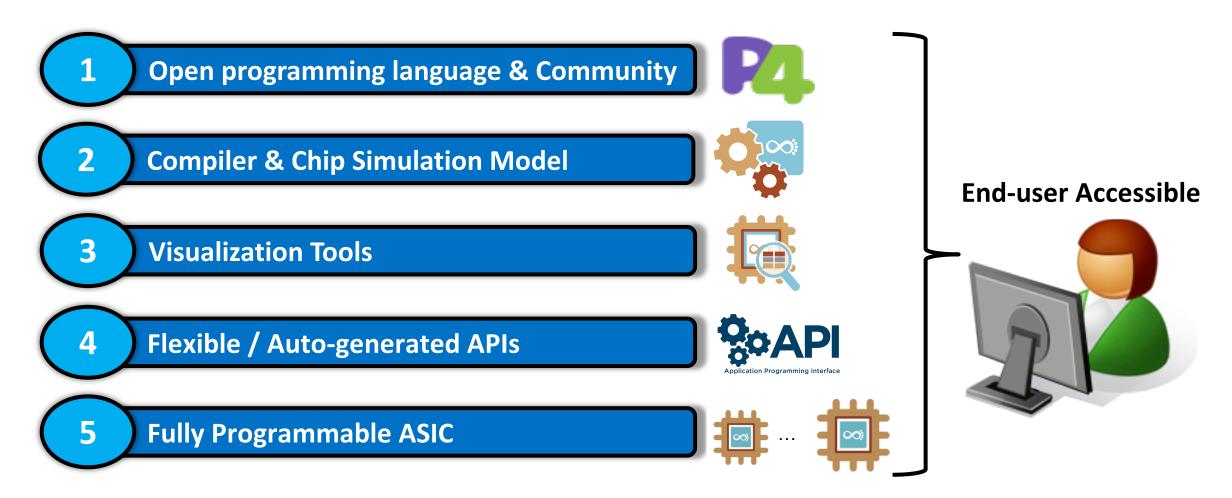

# Programmable Data Plane Building Blocks

# P4 vs Alternatives

| P4                                        | Alternatives                                            |

|-------------------------------------------|---------------------------------------------------------|

| Large open community /<br>ecosystem       | Little to zero community                                |

| Target / architecture independent         | Tied to specific ASIC                                   |

| High level language / generic constructs  | Constructs not re-usable                                |

| Designed for network pipeline programming | Designed for x86 applications and adapted to networking |

| Proven                                    | Not proven                                              |

# **Barefoot Baremetal Switch Ecosystem**

# Disaggregated Programmable Solution Building Blocks

| ASIC                               | Tofino  | Tofino2   |                 |                                     |     |          |

|------------------------------------|---------|-----------|-----------------|-------------------------------------|-----|----------|

| P4 Data<br>Plane<br>Provider       | ODM     | Barefoot  | End<br>Customer | 3 <sup>rd</sup> Party<br>Consultant |     |          |

| Control<br>Plane / NOS             | Stratum | SONiC     | Commercial      | Other /<br>custom                   |     |          |

| System<br>Vendor<br>(OEM /<br>ODM) | Stordis | Edge-core | Inventec        | Ufi Space                           | DNI | Embedway |

(intel)

ntel

10

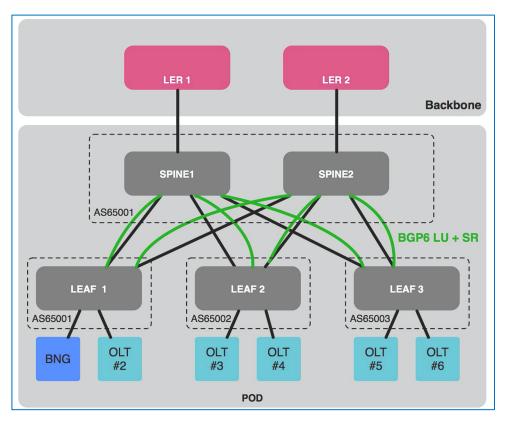

# **Use-case: Flexible Scaling**

- Different table sizes for leaf and spine

- Different table sizes for different deployments

- Update with changing network conditions

- Example: IPv4 vs IPv6 heavy fabric

| Parameter       | Scenario 1 | Scenario 2 |

|-----------------|------------|------------|

| IPv4 Host Local | Heavy      | Light      |

| IPv4 LPM        | Light      | Heavy      |

| IPv6 Host       | Heavy      | Light      |

| IPv6 LPM        | Light      | Heavy      |

# **Use-case: Cloud Gateway**

- Details

- IPv6 GRE gateway solution

- Migration from DPDK / OpenFlow

- Whitebox switch + ONL

- Custom P4-16 data plane, controlled via program APIs using GRPC

- Custom SDN controller

- Benefits

- Higher performance

- Flexibility and control

# UCLOUD

# Use-case: Baremetal Server Hosting with SONiC

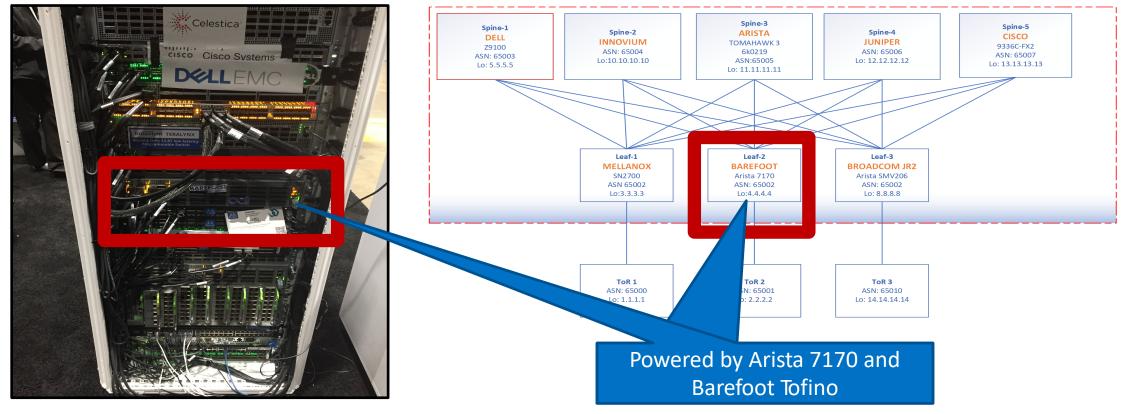

#### Joint demo with Microsoft and Arista

# **Use-case: Network Packet Brokers**

- Data plane & API Simplification

- Header Stripping

- Packet Slicing

- Flexible Tunnel Encapsulation / Decapsulation

- Enhanced load-sharing (weighted, GTP correlation)

- Flexible TCAM table scaling for policies

# **Use-case: Emerging Technologies**

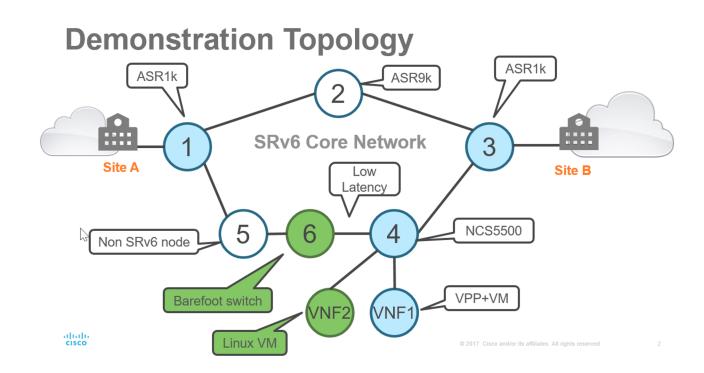

SRv6 endpoint and transit node functionality

Tofino performs large scale **PPPoE** session termination