During a recent P4.org open source developer days Ryan Goodfellow was invited to give a talk and demo about an independently developed open source P4 compiler built by a team at Oxide Computer Company. This blog is an overview of his presentation.

==========================

Background

A rack scale computer is hardware and software designed together such that they are delivered vertically integrated, providing ease and agility in scaling. Specifically a rack scale computer is custom-designed from the ground-up rather than assembling disparate network components in a rack and is targeted for installation in large enterprise data centers. Oxide leverages P4 programmable switches in the design of their rack scale computer and is working toward incorporation of P4 programmable NICs.

Why P4

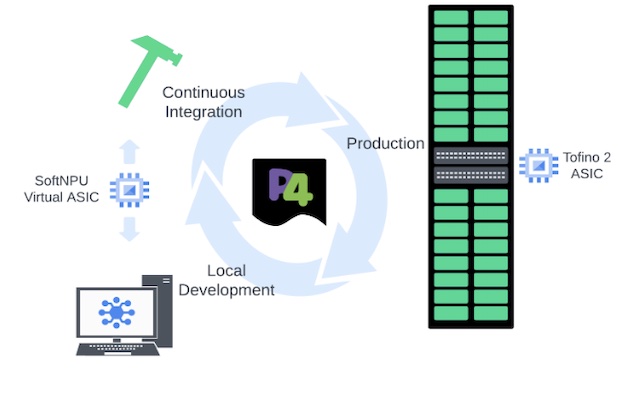

Using P4 enables Oxide to leverage programmability in the core of their networks while still maintaining test and CI-driven workflows. One of the primary challenges of building a product around P4 is integrating P4-programmable elements into a broader hardware/software system and testing at the scale and complexity the Oxide system is designed to operate at in a virtualized setting, as doing so physically is not economically feasible.

The advantage of network programmability is that it provides organizations with maximum flexibility, the ability to fine tune utilization of limited resources and the ability to better understand network behaviors and solve problems quickly to keep mission critical networks running.

Comprehensibility is simultaneously one of the biggest benefits and challenges of building systems with P4. When a system is built on P4 and you want to understand how the network functions, you can go read the code and understand the logical processing that happens by walking a call chain of parser and control blocks. This is an enormous step forward from fixed function ASICs where execution semantics are opaque to both system developers and network operators. However, we still have a long way to go with comprehensibility. The P4 specifications leave many details up to ASIC implementations, and the compilers and underlying instruction sets in today's P4 ecosystem for hardware targets are closed source. This leaves a knowledge gap between the logical intent of P4 programs and the execution semantics that result from compilation into the target ASIC's execution format. It makes it impossible to tell the difference between logical bugs in complex P4 programs versus compiler bugs. When undefined behavior occurs, there is no low-level architectural state akin to x86 or ARM registers to inspect, or machine instructions with well defined semantics to reason about. Architectural definition at the hardware-software interface is a fundamental building block for a robust and open ecosystem to take hold because it makes program execution comprehensible. So we view comprehensibility as both benefit and challenge number one in the P4 ecosystem.